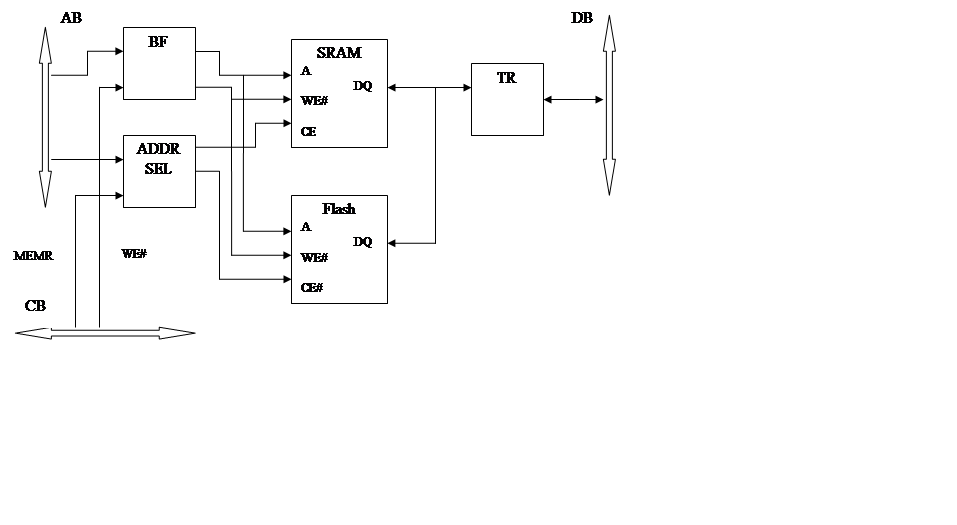

A – входы адреса микросхем памяти;

CE, CE# - входы выбора кристалла разных уровней активности;

WE# - сигнал разрешения записи;

DQ – двунаправленные входы/выходы данных.

Рис.2. Структурная схема памяти.

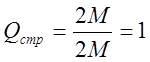

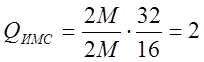

Определяем число микросхем памяти каждого типа в накопителе.

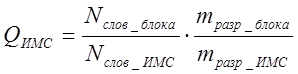

Общая формула для подсчёта необходимого количества микросхем:

.

.

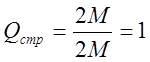

Количество необходимых физических страниц рассчитывается по формуле:

.

.

Здесь Nслов_блока – количество слов, хранимых блоком;

Nслов_ИМС - количество слов выбранной ИМС памяти;

mразр_блока – разрядность разрабатываемого блока;

mразр_ИМС – разрядность выбранной ИМС памяти.

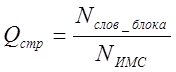

Для памяти SRAM:

.

.

.

.

Это означает, что потребуется 2 ИМС памяти SRAM, при этом количество физических страниц будет равно 1.

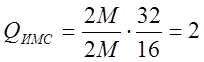

Для памяти Flash:

.

.

.

.

Это означает, что потребуется 2 ИМС памяти Flash, при этом количество физических страниц будет равно 1.

Т.к. для обоих типов памяти количество физических страниц равно 1, то дешифратор не требуется.

4. Разработка адресного селектора.

Основная функция адресного селектора заключается в выявлении факта обращения процессора (анализ сигнала MEMR) к памяти и определении области (SRAM или Flash), в которую направлено это обращение (анализ некоторых битов шины адреса). Дополнительной функцией адресного селектора является формирование флага «обращение по недействительному адресу». Этот флаг формируется адресным селектором в случае попадания физического адреса в пока не занятую область адресного пространства. Адресный селектор должен формировать сигналы выбора кристалла для обоих типов памяти. Кроме того, адресный селектор должен формировать сигнал OE#, разрешающий работу трансивера. Трансивер должен быть активным в том случае, когда выбрана для работы SRAM или Flash-память. С учётом составленной выше карты памяти, получаем формулы для формирования сигналов CE (для SRAM) и CE# (для Flash) и сигнала «обращение по недействительному адресу» (обозначим его Fl):

![]()

![]()

![]()

![]() .

.

Следует отметить, что сигнал «обращение по недействительному адресу» имеет смысл лишь в том случае, если в рассматриваемой гипотетической системе нет какой-либо другой памяти, под которую выделено адресное пространство из областей «запаса» (рис.2). Этот сигнал отправляется процессору через системную шину управления.

5. Выбор интерфейсных элементов.

Для выбора интерфейсных элементов необходимо рассчитать нагрузку, создаваемую микросхемами накопителей на линии адреса, данных и управления.

Выбранные микросхемы памяти выполнены по схемотехнологии КМОП. Токовая нагрузка, создаваемая этими микросхемами, мала (единицы микроампер) (в том числе малы токи утечки буферов, находящихся в z-состоянии) и ей можно пренебречь. Поэтому сразу переходим к расчёту ёмкостной нагрузки.

Для расчёта ёмкостной нагрузки нам потребуются справочные нормы ёмкостных параметров микросхем памяти, взятые из технической документации. Ниже, в таблицах 1 и 2 приведены эти значения для памяти SRAM и Flash соответственно.

Таблица 1. Ёмкостные параметры памяти SRAM.

|

Параметр |

Условия тестирования |

Максимальное значение |

Единица измерения |

|

CIN |

TA=25oC, f=1 МГц, VCC=3.3В |

12 |

пФ |

|

COUT |

15 |

пФ |

Таблица 2. Ёмкостные параметры памяти Flash.

|

Параметр |

Название |

Условия тестирования |

Типовое значение |

Максимальное значение |

Единицы измерения |

|

CIN |

Входная ёмкость |

TA=25oC, f=1 МГц, VIN=0В |

8 |

10 |

пФ |

|

COUT |

Выходная ёмкость |

TA=25oC, f=1 МГц, VOUT=0В |

8.5 |

12 |

пФ |

|

CIN2 |

Ёмкость по управляющим входам |

TA=25oC, f=1 МГц, VIN=0В |

8 |

10 |

пФ |

|

CIN3 |

Ёмкость по входам RESET# и WP#/ACC |

TA=25oC, f=1 МГц, VIN=0В |

20 |

25 |

пФ |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.