Федеральное Агентство по Образованию

Государственное образовательное учреждение

Высшего профессионального образования

Новосибирский Государственный Технический Университет

Кафедра Вычислительной Техники

«Разработка памяти»

Группа: АМ-411

Студент: Клещенев М.И.

Преподаватель: Михашов А.И.

Новосибирск 2006 г.

Оглавление

Техническое задание……………………………………………………. 4

Выбор элементной базы………………………………………………… 4

Шинный интерфейс……………………………………………………… 4

Разработка структурной схемы памяти………………………………… 4

Расчёт количества необходимых микросхем памяти…………………. 5

Составление карты памяти……………………………………………… 5

Разработка адресного селектора………………………………………… 6

Выбор интерфейсных элементов………………………………………… 7

Разработка функциональной схемы памяти……………………………. 9

Расчёт временных параметров…………………………………………… 11

Заключение……………………………………………………………….. 13

Список используемой литературы………………………………………. 14

Приложение 1 “Техническая документация к памяти SRAM”

Приложение 2 “Техническая документация к Flash памяти”

Введение

Разработка памяти включает в себя несколько этапов:

· получение технического задания;

· выбор номиналов микросхем памяти, отвечающих требованиям технического задания;

· выбор номиналов микросхем, выполняющих функции интерфейсных элементов (они также должны удовлетворять требованиям технического задания);

· расчёт нагрузки (токовой, ёмкостной), создаваемой микросхемами памяти на линии функционального назначения;

· расчёт временных параметров разработанной памяти (время доступа, время цикла);

· расчёт энергопотребления (в случае необходимости, если оно лимитировано в техническом задании).

Если рассчитанные параметры не удовлетворяют требования технического задания, то либо принимается решение о выборе других номиналов микросхем, либо данная ситуация должна быть оговорена разработчиком (как может повлиять на функционирование разработки отклонение тех или иных параметров, и на сколько существенно отклонение параметров)

При разработке также необходимо учитывать особенности конкретных типов памяти (например, для перепрограммируемой памяти нужно описать режимы программирования и стирания).

Цель работы:

Целью данной расчётно-графической работы является разработка резидентной памяти, функционирование которой должно максимально соответствовать техническому заданию.

Техническое задание:

Разработать память, состоящую из 2 видов: SRAM (статическая оперативная) и Flash File(с файловой организацией). Данная память должна включаться в трех шинную системную магистраль, состоящую из шины адреса (AB), шины данных (DB) и шины управления (CB).

· Объём памяти SRAM – 4 Mб, разрядность – 32 бит информационная организация (1Мх32)бит).

· Объём памяти FF – 8 Mб, разрядность – 32 бит (информационная организация (2Мх32)бит).

· Обеспечить время циклов чтения и записи не более 150 нс. Электрический интерфейс ТТЛ.

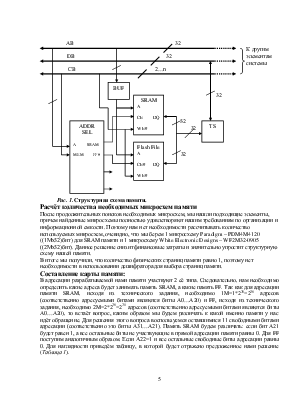

Для реализации схемы выберем в качестве номинала:

Техническая документация с описанием выбранных микросхем находится в приложении 1 и 2

Шинный интерфейс:

Исходя из технического задания мы должны обеспечить доступ памяти к трех шинной системной магистрали.

Так как информационная организация памяти типа SRAM и FF – 1Мх32 и 2Мх32, то для адресации памяти мы должны обеспечит 32-х битную шину адреса (AB) и 32-ти битную шину данных (DB). Также для управления памятью необходимо использование шины управления (CB) с которой будут поступать сигналы:

Не исключено что в процессе разработки памяти нам придётся включить в шину управления дополнительные сигнальные линии, введение которых будет обусловлено особенностями функциональной схемы памяти и особенностями выбранных типа номиналов. Поэтому разрядность шины управления мы определим позднее.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.