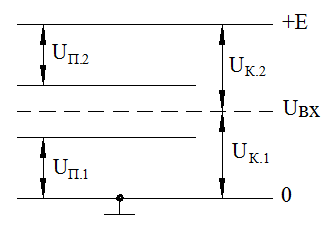

а для p-канального VT1 – до шини живлення. Тому діаграма напруг керування ключом має вигляд, приведений на рис.2.12, де UК.1 = UВХ - напруга керування транзистором VT1, а UК.2 =Е - UВХ – напруга керування транзистором VT2. Враховуючи що для кожного транзистора UП є постійною величиною в залежності від величини напруги Е можливі різні співвідношення між напругою живлення Е та пороговими рівнями:

а) E > UП.1 + UП.2;

б) E < UП.1 + UП.2; (2.16)

в) E = UП.1 + UП.2.

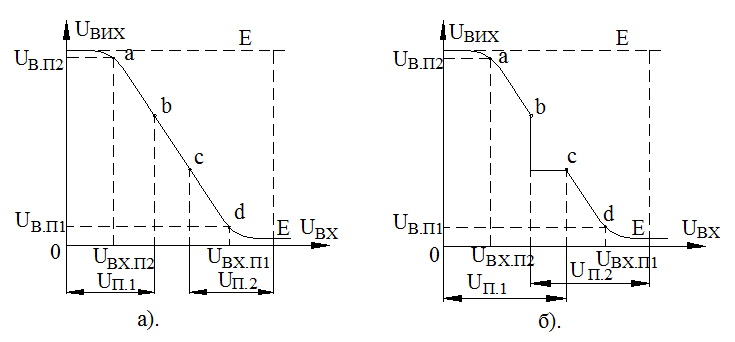

Передаточні характеристики UВИХ

= f(UВХ) для випадків а) та б) приведені на рис.2.13. Випадок в)

реально реалізувати неможливо, так як неможливо точно задати UП.1

та UП.2.

Передаточні характеристики UВИХ

= f(UВХ) для випадків а) та б) приведені на рис.2.13. Випадок в)

реально реалізувати неможливо, так як неможливо точно задати UП.1

та UП.2.

Конкретні значення високого і низького рівнів вихідної напруги ключа визначаються співвідношенням опорів закритого транзистора R3, та відкритого RВ Реально R3 >> RВ, тому напруга високого рівня практично рівняється

Рис.2.12. напрузі живлення, а низького - майже не відрізняється від нуля. При зміні вхідної напруги від нуля до UП.1 транзистор VT2 закритий. В той же час відповідно до (2.16,а) транзистор VT3 з відкритого стану з практично нульовою напругою на ньому переходить при UВХ.П2 з пологої характеристики на круто падаючу. При подальшому підвищенні UВХ до UП.1 відкривається транзистор VT2 і спочатку буде знаходитись на пологих характеристиках. При підвищенні UВХ напруга UЗ.2 на затворі VT2 зменшується відповідно до формули:

і транзистор буде підтримуватись в відкритому стані пока

UВХ < Е – UП.2.

UП.1 < UВХ < Е – UП.2

обидва транзистори будуть знаходитись у відкритому стані і через них буде протікати прохідний струм (інтервал bс). Коли UВХ досягне рівня Е – UП.2 транзистор VT1 закриється і струм через транзистори припиниться. Подальше підвищення UВХ приведе до переходу транзистора VT2 до відкритого стану.

Як приклад, розглянемо ситуацію, коли Е=10В, UП.1=5В, UП.2=4В. Тоді в інтервалі вхідних напруг

5 < UВХ < 10 – 4= 6

обидва транзистори будуть знаходитись у відкритому стані.

Рис.2.13.

Розглянемо тепер ситуацію, яка має місце при виконанні співвідношення 2.16.б, коли сума порогових рівнів перевищує напругу живлення Е. (рис..2.13.б)

При підвищенні вхідної напруги до величини UВХ=Е – UП.2 транзистор VT1 закривається. Транзистор VT2 буде знаходитись в закритому стані до того моменту, поки UВХ < UП.1. Коли UВХ =UП.1 транзистор VT2 відкривається і після того, як вхідна напруга стане більшою рівня UВХ.П.1 переходить в режим круто падаючих характеристик з практично нульовим рівнем вхідної напруги. Прохідний струм в такій схемі не появляється.

14.Враховуючи той факт, що порогові рівні для кожного транзистора являються величинами постійними, то кожен з режимів може мати місце, якщо змінювати напругу живлення. Режим б) як видно з аналізу, корисний з тої точки зору, що транзисторний ключ ні в статичних режимах, ні при зміні стану не споживає струму (якщо не враховувати наявність паразитних конденсаторів). При підвищенні напруги живлення схема переходить в режим а), за яким, як буде показано пізніше, можуть появитись аварійні режими.

Часові співвідношення розглянутого ключа при зміні його станів набагато кращі, ніж ключа з резистивним навантаженням. Перш за все це пояснюється тим що в процесі зарядки паразитних конденсаторів відсутній високоомний опір RС і перезаряд їх переходить через відкриті транзистори VT1 і VT2. Слід зазначити, що час перемикання ключа суттєво залежить від величини порогових рівнів і крутизни характеристики І3=f(UВЗ) транзисторів, які є технологічними параметрами і можуть покращуватись з удосконаленням технологій виробництва інтегральних схем.

2.3 Технічні характеристики базових логічних елементів

і особливості їх використання

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.