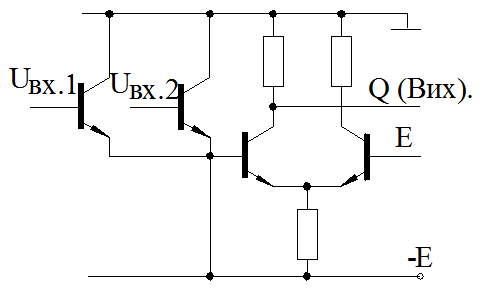

На рис.2.42 приводиться схема, в якій поряд з операціями інверсії по виходах y1 i y2, виконується операція АБО - НІ

|

Рис.2.42. що інтегральні логічні елементи мають

мінімальну кількість напровідникових елементів та внутрішніх з’єднань.

Схеми не мають в своєму складі складних в технологічному плані елементів-

резисторів. Все це дозволяє підвищувати рівень інтеграції в фактично

стандартному технологічному процесі біполярної транзисторної логіки. Підвищення

швидкодії елементів І2Л технології досягається за рахунок переходу

на транзистори Шоткі.

Рис.2.42. що інтегральні логічні елементи мають

мінімальну кількість напровідникових елементів та внутрішніх з’єднань.

Схеми не мають в своєму складі складних в технологічному плані елементів-

резисторів. Все це дозволяє підвищувати рівень інтеграції в фактично

стандартному технологічному процесі біполярної транзисторної логіки. Підвищення

швидкодії елементів І2Л технології досягається за рахунок переходу

на транзистори Шоткі.

На сьогоднішній день використання І2Л технології обмежене. В вітчизняній практиці на її основі виготовляються лише декілька видів мікросхем. Це мікросхеми пам’яті серії 541

Рис.2.43.

(541РУ1А, 541РУ21 - мікросхеми статичних оперативних запам’ятовуючих

пристроїв; 541РЕ1 - постійний програмуємий запам’ятовуючий пристрій

масочного типу). Реальні технічні параметри, для порівняння з іншими

базовими логічними елементами слідуючи: tЗ ![]() 2

2![]() 3

нс; РСП

3

нс; РСП![]() 0,2 mВт; А

0,2 mВт; А![]() 0,1 пДж.

0,1 пДж.

В практиці відомих західноєвропейських та американських компаній технологія І2Л також не находить поки що широкого використання. Пояснюється це здебільшого значним прогресом в розвитку КМОН, та БІКМОН технологій.

2.3.7.Базові елементи емітерно - зв’язаної логіки (ЕЗЛ).

21.Базовий елемент ЕЗЛ

реалізується на основі перемикачів струму по схемі діфференціального

каскаду, який розглянутий в другому параграфі поточного розділу. Як

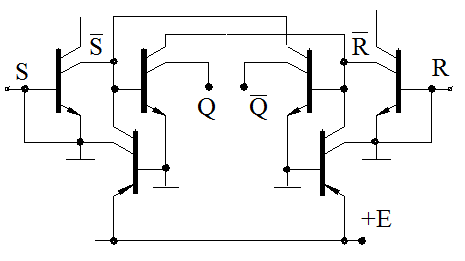

видно з схеми базового елементу (рис. 2.44, елемент серії К500)

логічна функція 2АБО - НІ реалізується на базі паралельно з’єднаних

транзисторів VT1 і VT4, що недопустимо в

21.Базовий елемент ЕЗЛ

реалізується на основі перемикачів струму по схемі діфференціального

каскаду, який розглянутий в другому параграфі поточного розділу. Як

видно з схеми базового елементу (рис. 2.44, елемент серії К500)

логічна функція 2АБО - НІ реалізується на базі паралельно з’єднаних

транзисторів VT1 і VT4, що недопустимо в

Рис.2.44. практиці з-за проблеми перехоплення струму.

В ЕЗЛ перехоплення струму не з’являється через наступні причини:

· пороговий рівень напруги різних логічних елементів задається зовнішнім джерелом напруги E0, яке встановлюється з високою точністю і стабілізується в широкому температурному діапазоні;

· - вхідний опір розглядаємих схем значно вищий, ніж схем

насичених ключів завдяки наявності емітерного резистора R6.

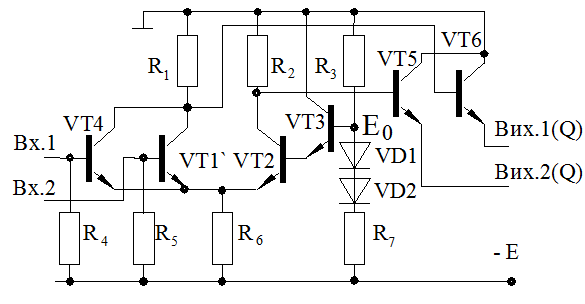

Рис.2.45.

Рис.2.45.

Вихідні емітерні повторювачі по інверсному і прямому виходах, виконані на транзисторах VT5, VT6, забезпечують формування струму навантаження з запасом, достатнім для швидкого перезаряду ємностей навантаження.

На рис. 2.45, а приведена схема підключення логічного елемента. Навантаження R1 та R2 використовуються лише в тому випадку, якщо елемент являється кінцевим каскадом.. На рис. 2.45,б приведені характеристики перемикання для прямого та інверсного виходів. З них витікає, що логічні рівні ЕЗЛ змінюються в внтервалі –0.8 ¸ -1.7 В. Рівні U1вих = 0.8 В; U0вих =-1.7 В.

Низький рівень логічного перепаду призводить до малої статичної перешкодостійкості мікросхем.

Враховуючи лінійний режим

роботи транзисторів, в забезпеченні перешкодостійкості важливу роль

відіграє опорна напруга Е0. В схемі, приведеній на

рис 2.44 вона задається ланцюгом R3, VD1, VD2, R7 і в деякій

мірі залежить від напруги живлення. В подальших серіях мікросхем

(наприклад, серії К1500) використовуються спеціальні схеми, які

забезпечують високу стабільність Е0 при зміні

температури та напруги живлення.

Враховуючи лінійний режим

роботи транзисторів, в забезпеченні перешкодостійкості важливу роль

відіграє опорна напруга Е0. В схемі, приведеній на

рис 2.44 вона задається ланцюгом R3, VD1, VD2, R7 і в деякій

мірі залежить від напруги живлення. В подальших серіях мікросхем

(наприклад, серії К1500) використовуються спеціальні схеми, які

забезпечують високу стабільність Е0 при зміні

температури та напруги живлення.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.