Рисунок 4.2 – Схема начального сброса

Для сброса процессора необходимо кратковременно нажать на кнопку S1, при этом происходит короткое замыкание емкости C1 в следствии чего он почти мгновенно разряжается, на входе RESET образуется логический 0. При отпускании кнопки происходит заряд емкости, при этом потенциал на RESET возрастает с низкого уровня до высокого за некоторое время. Рассчитаем время нарастания по следующей формуле:

![]()

Закон нарастания напряжения в интегрирующей RC-цепочке:

, откуда

, откуда

При R=10 кОм, U=2В, Еп=5В:

R1=10 кОм, С1=39.15 нФ.

4.1.2 Блок тактовой синхронизации

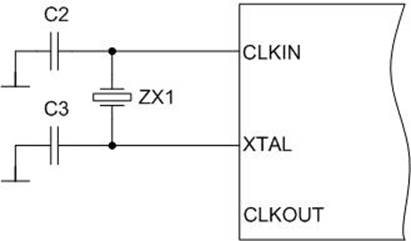

Для работы процессора необходим внешний источник сигналов тактовой синхронизации, в качестве которого используется кварцевый резонатор ZQ1. Схема подключения резонатора показана на рисунке 4.3

Рисунок 4.3 – Схема блока тактовой синхронизации

Номинальная резонансная частота ZX1 не должна превышать половину предельной допустимой частоты процессора. Т.к. частота процессора 10 МГц (ТЦ=100 нс), то резонансная частота резонатора выбирается не более 5 МГц.

Конденсаторы С2 и С3 выбираются керамическими с номиналом 20 пФ.

4.1.3 Сопряжение с линией

Сопряжение с линией происходит тремя согласующими устройствами:

1) дифференциальная система, предназначенная для преобразования двухпроводного окончания линии в четырехпроводное, с раздельными цепями приема и передачи;

2) фильтр нижних частот с разделительными конденсаторами на входе АЦП;

3) операционный усилитель на выходе ЦАП для преобразования дифференциального сигнала в однополярный.

Передача по линии идет в полудуплексном режиме, т.е. передача и прием разделены по времени. Это упрощает схему диф. системы, т.к. попадание сигнала с передачи (от ЦАП) на прием (на АЦП) не критично для работы системы целом (при передачи сигнала запрещается прерывание от АЦП), поэтому разработка схемы эхоподавления не требуется.

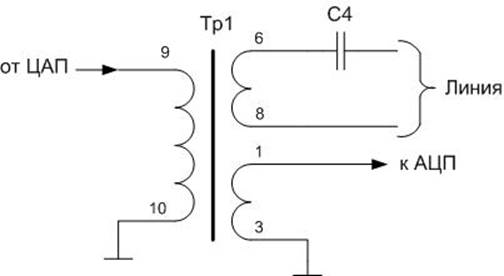

Схема диф. системы представлена на рисунке 4.4. В качестве Тр1 используется трансформатор типа Т2-21, разделительная емкость С4=2.2 мкФ.

Рисунок 4.4 – Схема дифференциальной системы

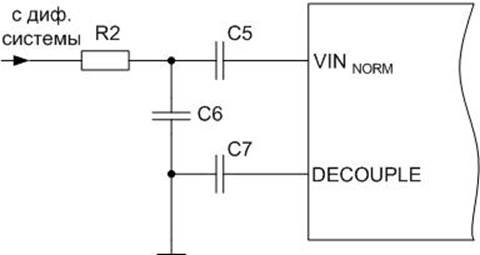

На входе АЦП необходимо установить ФНЧ RC типа с добавлением разделительных конденсаторами. Схема цепи показана на рисунке 4.5.

Расчет конденсаторов С5 и С7 ведется по следующей формуле:

, где

, где

f1=30 Гц – частота среза,

RIN=200 кОм – входное сопротивление АЦП.

Расчет RC фильтра. Частота среза fср=20 кГц, R2=1 кОм. С6 рассчитывается по формуле:

Рисунок 4.5 – Схема согласования с АЦП

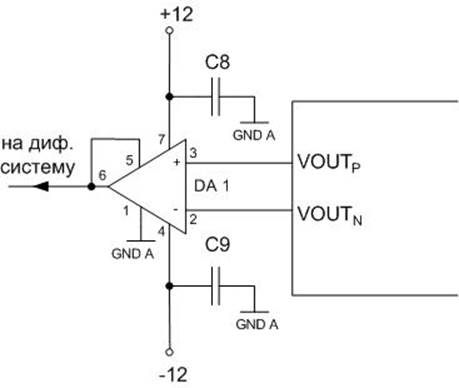

С выхода ЦАП дифференциальный сигнал преобразуется в однополярный при помощи операционного усилителя (рисунок 4.6).

Рисунок 4.6 – Схема согласования с ЦАП

В качестве ОУ используется микросхема SSM2141 Analog Devices (DA1). Данная схема включения ОУ является стандартной и осуществляет подавление синфазной помехи на 100 дБ. Для парафазного сигнала действует формула: E0=EP - EN , коэффициент усиления при этом равен 1.

Емкости C8 и С9 берем равными 0.1 мкФ.

4.2 Выбор комплектующих схемы

На рисунке 4.7 представлена полная принципиальная схема разрабатываемой микропроцессорной системы приемника двух сигнальных частот многочастотной системы сигнализации.

Перечень используемых элементов представлен в таблице 4.1.

Таблица 4.1 – Перечень используемых элементов

|

Поз. обозн. |

Наименование |

Кол. |

Примечание |

|

C1, C2 |

MCC-NPO-10v-20pF |

2 |

|

|

C3 |

MCC-NPO-10v-3900pF |

1 |

|

|

C4, C5 |

MCC-Y5V-50v-0,1uF |

2 |

|

|

C6, C7 |

MCC-NPO-10v-3000pF |

2 |

|

|

C8 |

MCC-NPO-10v-7800pF |

1 |

|

|

C9 |

MCC-Y5V-10в- 2.2uF |

1 |

|

|

DD1 |

ADSP-21msp58 |

1 |

|

|

DA1 |

SSM2141 |

1 |

|

|

R1 |

МЛТ-0,125-10 кОм |

1 |

|

|

R2 |

МЛТ-0,125-1 кОм |

1 |

|

|

S1 |

КМД1-I |

1 |

|

|

Tp1 |

Т2-21 |

1 |

|

|

XP1 |

DB-15S |

1 |

|

|

ZX1 |

RV-26 5.0 МГц |

1 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.