Рисунок 3.1 – Блок схема main

Подпрограмма on вызывается по прерыванию от IRQ2. Производит необходимую инициализацию (0) и осуществляет вызов подпрограммы dac с параметром B1. После выполнения dac происходит возрат в основную программу.

Рисунок 3.2 – Блок схема on

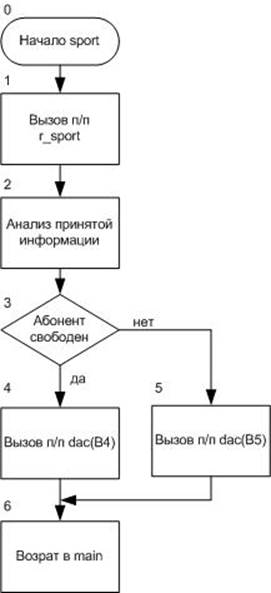

Подпрограмма sport (рисунок 3.3) вызывается прерыванием от SPORT при появлении данных на порту. После инициализации (0) вызывается подпрограмма приема информации с порта (1) – r_sport. После завершения который производится анализ принятой информации (2) и проверяется на условие (3). В зависимости исхода вызывается подпрограмма dac с параметром В4 (4), либо с параметром В4 (5). После выполнения dac происходит возрат в основную программу.

Рисунок 3.3 – Блок схема sport

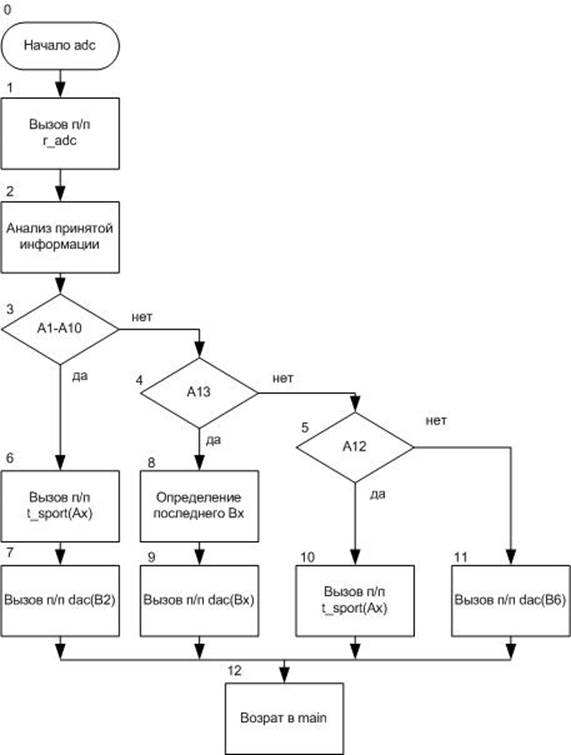

Подпрограмма adc (рисунок 3.4) вызывается прерыванием от ADC. При этом происходит инициализация (0). Вызов подпрограммы r_adc для приема информации с порта (1). Далее происходит анализ принятой информации (2) и блоками 3-5 осуществляется проверка на условия. Если принятая информация соответствует цифрам номера (А1-А10), то осуществляется выдача на SPORT принятой цифры Ах при помощи подпрограммы t_sport (6). Далее осуществляется запрос следующей цифры вызывом подпрограммы dac с параметром B2 (7). Если принялся сигнал А13, то происходит определение предыдущего переданного сигнала Вх (8) и вызывается подпрограмма dac с параметром Вх (9). Если принялся сигнал А12, то осуществляется передача его в последовательный порт подпрограммой t_sport (10). Если в итоге не опознался сигнал, то происходит вызов подпрограммы dac с параметром В6. После выполнения блоков 7, 9, 10, 11 происходит возрат в основную программу (12).

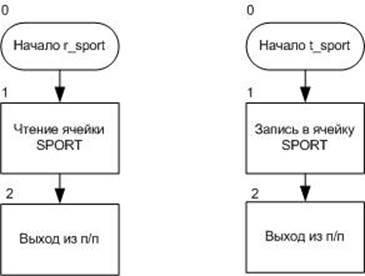

На рисунке 3.5 показаны блок схемы подпрограмм передачи и приема информации с последовательного порта.

Рисунок 3.4 – Блок схема adc

Рисунок 3.5 – Блок схемы r_sport и t_sport

Подпрограмма r_adc осуществляет спектральный анализ сигнала с помощью быстрого преобразования Фурье (БПФ) – разложение в ряд Фурье принимаемого сигнала. Осуществляет обнаруживания частот “2из6” в общем спектре и возвращает из подпрограммы значение частот. Для БПФ используется 256-точечный алгоритм БПФ radix-2.

Подпрограмма dac осуществляет выработку двухчастотного сигнала нужных частот и выдачей его на порт DAC.

3.2 Распределение адресного пространства

В процессоре используется Гарвардская архитектура, для которой характерно разделение памяти данных и памяти программ. Распределение адресного пространства заключается в конфигурировании памяти данных и памяти программ.

Конфигурация памяти программ. Конфигурация осуществляется состоянием вывода MMAP, определяющий два типа конфигурации памяти программ. В нашем случае MMAP=1, при этом слова внешней памяти программ начинаются м нулевого адреса (0х0000), а внутреннее ОЗУ занимает 2К слов, начиная с 0х3800.

Внутреннее ОЗУ программ имеет достаточно высокое быстродействием для извлечения команд и данных в том же цикле, что исключает необходимость использования кэш-памяти.

В процессоре имеется программируемое ПЗУ которое будет использоваться для хранения кода программы и необходимых данных, например массивы коэффициентов для формирования аналогового сигнала. Для активизации ППЗУ бит ROMENABLE в регистре управления состояниями ожидания памяти данных должен быть установлен в 0.

Будет использоваться автономный режим работы ППЗУ, это значит что при рестарте программа стартует с адреса 0х0800, т.е. с начального адреса ППЗУ, при этом активизация ППЗУ происходит автоматически. Для включения этого режима необходимо на вывод BMODE подать высокий уровень сигнала (1).

Это позволяет обойтись без использования внешней памяти для начальной загрузки, но требуется копирование таблицы векторов прерывания в адрес 0х0800. Внешняя память программ также не используется.

Конфигурация памяти программ представлена на рисунке 3.6 а.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.