После осуществлений необходимых действий происходит возврат в main командой RTI.

Подпрограмма r_adc.

Осуществляет прием данных с порта АЦП и преобразует принятые данные в номер сигнала.

Вызовом подпрограммы radix-2 мы производим прием с порта АЦП информации и при помощи быстрого преобразования Фурье делаем спектральный анализ сигнала. Номера принятых частот сохраняются в регистрах AX0 и AY0.

Номер сигнала получается суммированием номеров частот, но при этом учитывается что частоты 4 и 7 означают сигнал 10, а не 11.

Подпрограмма возвращает в main номер принятого сигнала.

Подпрограмма dac.

Подпрограмма осуществляет формирование необходимого сигнала и передачу его в порт ЦАП.

При инициализации описываются файлы с массивами значений данных для формирования сигнала. Для каждого сигнала имеется свой массив данных.

В начале происходит очистка всех регистров управления с адресами 0x3FEF по 0x3FFЕ при помощи цикла.

Производим маскирование прерываний от SPORT0, IRQ2 и аналогового интерфейса, при этом разрешаем прерывание от таймера командой IMASK=0x001; (по выходе из подпрограммы dac вновь производим маскирование прерывание от таймера и разрешение необходимых командой IMASK=0х229;).

Далее идет определение номера передаваемого сигнала при помощи логической операции исключающая или и проверки на условие результат АЛУ равен 0, при определении происходит прыжок по соответствующей метке на код программы, где присваивается начальный адрес кольцевого буфера и загружается регистр AX0 значением, которое будет в будущем загружено в TPERIOD и TCOUNT, это значение рассчитывается из следующей формулы:

fс – частота сигнала с большим номером;

Тцикл – длительность цикла процессора, 100 нс.

Там же загружается собственное для каждого сигнала значение счетчика, для организации в будущем цикла формирования сигнала с длительностью 68 мс, это значение рассчитывается по следующей формуле:

![]()

tсигнала = 68 мс.

Далее происходит возврат и продолжается настройка генератора адреса. После этого происходит непосредственная настройка таймера – загрузка регистров TPERIOD и TCOUNT, разрешения прерывания от таймера, прерывание без вложения с реакцией на перепад и включение таймера.

Далее организуется цикл, за каждый проход цикла выполняется одно прерывание, таким образом соблюдается длительность 68 мс.

По завершению цикла происходит сохранение в регистре AY1 значения передаваемого сигнала, для случая, если нам понадобится вновь его передавать. Выключаем таймер и выходим из подпрограммы.

4 РАЗРАБОТКА ФУНКЦИОНАЛЬНОЙ СХЕМЫ

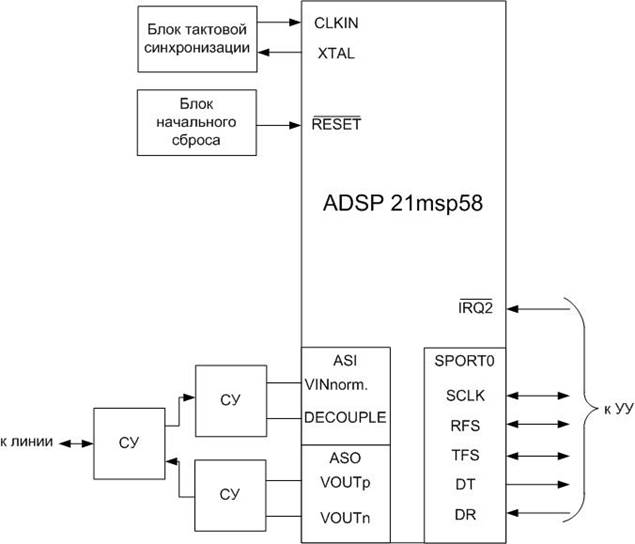

В качестве центрального узла системы является сигнальный процессор ADSP 21msp58, с реализацией на кристалле ОЗУ и ПЗУ, а также аналогового интерфейса. Учитывая особенности выбранного микропроцессора, а также аппаратно-программные решения, структурная схема приемника изменилась и имеет вид представленный на рисунке 4.1.

Рисунок 4.1 – Структурная схема приемника

Основным отличием от структурной схемы представленной на рисунке 2.2 является то, что добавлены 2 согласующих устройства: на вход АЦП RC-фильтр для осуществления теоремы Котельникова и на выход ЦАП устройства преобразующий диф. выход в однополярный.

Также показаны выводы микропроцессора используемые для связи с внешними устройствами. Не показаны выводы MMAP и BMODE предназначенные для конфигурации памяти и режима начальной загрузки.

4.1 Описание функциональных блоков

4.1.1 Блок начальной установки

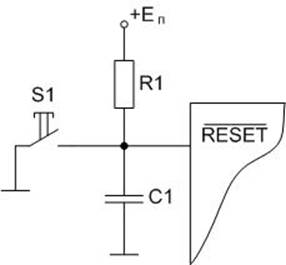

Для сброса процессора необходимо подать на вход RESET логический 0 – низкий уровень сигнала. Для установления процессора в исходное состояние необходимо удерживать низкий уровень сигнала на входе RESET минимум 2000 циклов процессора. Для этого используется интегрирующая RC цепочка, с помощью которой добиваются плавного нарастания напряжения на входе сброса. Принципиальная схема блока начального сброса представлена на рисунке 4.3.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.