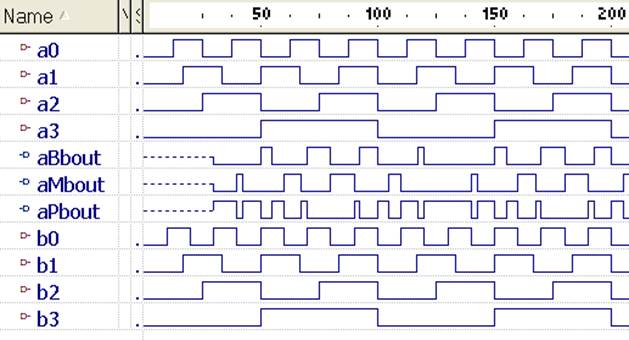

Waveform

Примечание: aBbout ≡

А > B ; aMbout ≡A < B ; aPbout ≡A

= B ;

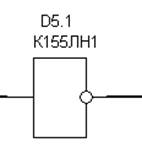

2.4 Логический элемент «НЕ» К155ЛН1

Задержка – 27нс

Задержка – 27нс

Таблица истинности

|

Input1 |

OutputInv |

|

0 |

1 |

|

1 |

0 |

Waveform

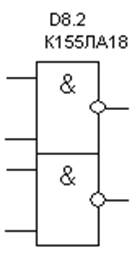

2.5 К155ЛА18 - два логических элемента «2И-НЕ»

Задержка – 27нс

Таблица истинности

|

Input1 |

Input2 |

Output_inv3 |

Input4 |

Input5 |

Output_inv6 |

|

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

1 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

1 |

0 |

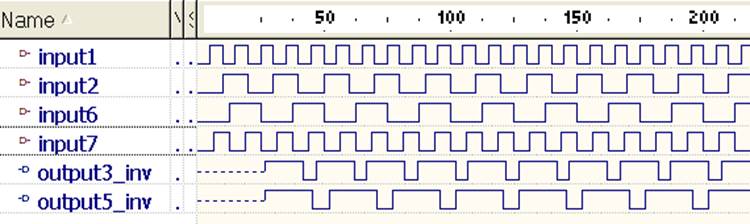

Waveform

2.6 К155ЛА3 - четыре логических элемента «2И-НЕ»

Задержка – 27нс

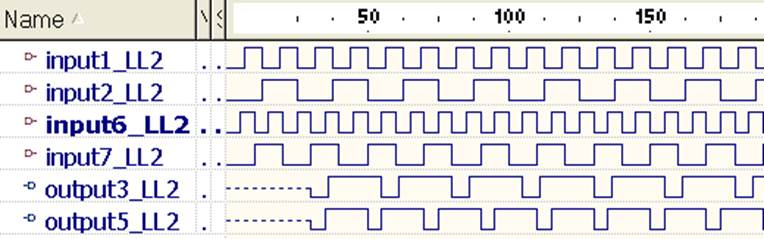

2.7 К155ЛЛ2 - два логических элемента «2ИЛИ»

Задержка

– 30нс

Задержка

– 30нс

Таблица истинности

|

Input1 |

Input2 |

Output3 |

Input4 |

Input5 |

Output6 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

Waveform

2.8 К155ЛЛ1 - четыре логических элемента «2ИЛИ»

Задержка – 30нс

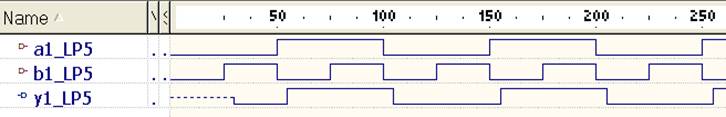

2.9 К555ЛП5 - четыре 2-входовых логических элемента Исключающее ИЛИ

Задержка – 30нс

Таблица истинности

|

Input1 |

Input2 |

Output3 |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Waveform

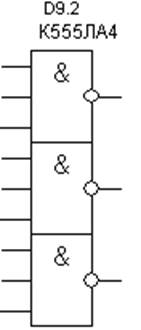

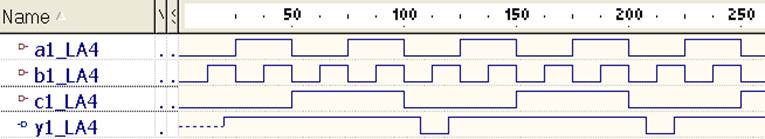

2.10 К555ЛА4 - три логических элемента «3И-НЕ»

Задержка – 20нс

|

Input1 |

Input2 |

Input3 |

Output4 |

|

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

Waveform

3. Описание элементов схемы на языке VHDL

-------------------------------k155tm2

--------------------------------- created by Design Wizard: 03/03/04 18:56:02

-library IEEE;

use IEEE.std_logic_1164.all;

entity k155tm2 is

port (

r_inv_T1: in STD_LOGIC;

d_T1: in STD_LOGIC;

c_T1: in STD_LOGIC;

s_inv_T1: in STD_LOGIC;

q_T1: out STD_LOGIC;

q_inv_T1: out STD_LOGIC;

r_inv_T2: in STD_LOGIC;

d_T2: in STD_LOGIC;

c_T2: in STD_LOGIC;

s_inv_T2: in STD_LOGIC;

q_T2: out STD_LOGIC;

q_inv_T2: out STD_LOGIC

);

end k155tm2;

architecture k155tm2 of k155tm2 is

begin

process (r_inv_T1,d_T1,c_T1,s_inv_T1)

variable state_T1,state_inv_T1:STD_LOGIC;

begin

if c_T1='1' and c_T1'event then

state_T1:=d_T1;

state_inv_T1:=not state_T1;

end if;

if r_inv_T1='0' and s_inv_T1='1' then

state_T1:='0';

state_inv_T1:='1';

end if;

if r_inv_T1='1' and s_inv_T1='0' then

state_T1:='1';

state_inv_T1:='0';

end if;

if r_inv_T1='0' and s_inv_T1='0' then

state_T1:='1';

state_inv_T1:='1';

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.