4. СИСТЕМНАЯ ПАМЯТЬ PC AT

г===========================================¬

¦ Организация оперативной памяти компьютера ¦

L===========================================Для организации эффективной работы работы микропроцессора при операциях чтения и записи в оперативной памяти (ОП) необходимо иметь разрядность ячеек памяти, равную формату слова микропроцессора.

Для машин, реализованных на микропроцессорах типа Intel 8086,

Intel 80286 и Intel 80386SX, необходимо иметь 16-разрядную память.

Память этих процессоров обычно имеет организацию в два байта

(старший и младший или нечетный и четный), а каждый байт имеет контрольный разряд паритета. Совокупность двух байтов памяти составляет банк памяти.

Количество банков памяти и тип DRAM определяют обьем памяти процессора.

Для машин, реализованных на микропроцессоре типа Intel 80386, разрядность ячеек памяти может быть как 16, так и 32 разряда. Для указания разрядности подключенной памяти на соответствующий контакт микропроцессора -BS16 необходимо подать уровень логического нуля

(16 разрядов) или единицы (32 разряда).

---------------------------¬

¦Адресации байтов в памяти ¦

L--------------------------- Процессор может выполнять как команды чтения или записи слова в память, так и команды записи или чтения одного байта. Особенностью архитектуры микропроцессоров семейства

Intel 80Х86 является механизм "перекоса байтов", который меняет местами старший и младший байты в слове внутри МП при работе c шиной.

При этом чтение из памяти шестнадцатеричных чисел форматом больше, чем один байт, представляет проблему в архитектуре IBM PC, корни которой уходят в отличия между арабским стилем записи справа налево, в котором мы привыкли записывать десятичные и двоичные числа (младшая цифра записывается справа, старшая - слева) и римским стилем записи чисел, в соответствии с которым

(согласно архитектурной концепции фирмы Intel) принято отображать действительные шестнадцатеричные байты: слева направо. При этом наиболее значащий байт записывается в ячейку памяти с наибольшим адресом. Таким образом, несмотря на то, что 16-разрядное число 1010 1101 0101 0111

эквивалентно шестнадцатеричному числу AD57, оно записывается (как слово из двух байтов) в обратном порядке - 57AD. При этом младший байт (57) слева, а старший байт (AD) - справа.

Эта конвенция не распространяется на старшую и младшую тетрады байта.

Если необходимо записать слово AD57 по адресу 724h, то по адресу 724h

запишется байт 57, а по адресу 725h - байт AD. Этот реверсивный порядок размещения слов в памяти прозрачен до тех пор, пока не возникает необходимость выполнить пословный дамп участка памяти или надо организовать управление системной шиной.

Необходимо учитывать "зеркальное" размещение информации в памяти при чтении структуры таблицы векторов прерываний и в особенности таблицы размещения файлов (FAT).

При передаче байта с нечетным адресом микропроцессор выдает специальный сигнал разрешения передачи старшего байта BHE.

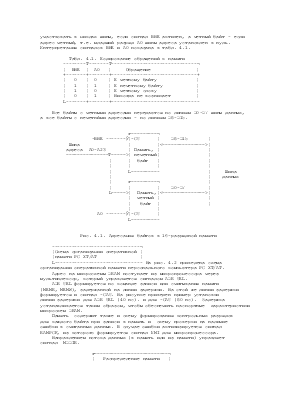

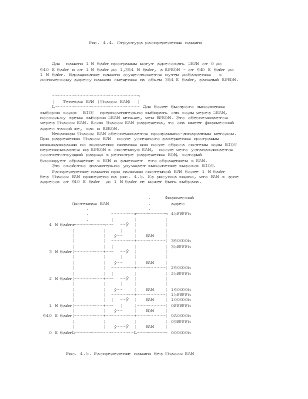

Структурная схема адресации байтов в 16-разрядной памяти приведена на рис.4.1.

Рассмотрим возможные случаи передачи байтов и слов с четными и нечетными адресами. Когда процессор передает байт с нечетным адресом, он формирует активный сигнал BHE и помещает на шину нечетный адрес.

При передаче же байта с четным адресом сигнал BHE пассивен, а на шине находится четный адрес. Передачи слов всегда включают в себя оба байта, поэтому сигнал BHE активный. Кроме того, при передачах слов на шину всегда выдается четный адрес. Это означает, что нечетный байт должен участвовать в циклах шины, если сигнал BHE активен, а четный байт - если адрес четный, т.е. младший разряд А0 шины адреса установлен в нуль.

Интерпретация сигналов BHE и A0 показана в табл. 4.1.

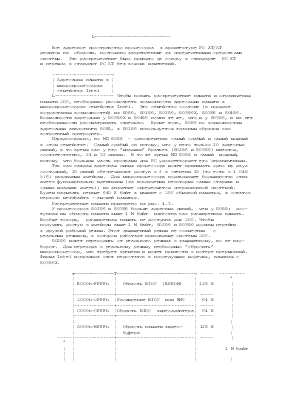

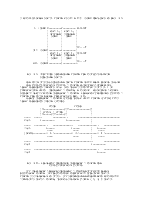

Табл. 4.1. Кодирование обращений к памяти

--------T-------T------------------------------¬

¦ BHE ¦ A0 ¦ Обращение ¦

+-------+-------+------------------------------+

¦ 0 ¦ 0 ¦ К четному байту ¦

¦ 1 ¦ 1 ¦ К нечетному байту ¦

¦ 1 ¦ 0 ¦ К четному слову ¦

¦ 0 ¦ 1 ¦ Никогда не возникает ¦

L-------+-------+------------------------------Все байты с четными адресами передаются по линиям D0-D7 шины данных, а все байты с нечетнйми адресами - по линиям D8-D15.

г=========¬

-BHE -------Ў¦-CS ¦ D8-D15 ¦

Шина ¦ ¦<===============>¦

адреса А0-А23 ¦ Память, ¦ ¦

===============T=====>¦ нечетный¦ ¦

¦ ¦ байт ¦ ¦

¦ ¦ ¦ ¦

¦ L=========- ¦ Шина

¦ ¦ данных

¦ г=========¬ ¦

¦ ¦ ¦ D0-D7 ¦

L=====>¦ Память,¦<===============>¦

¦ четный ¦ ¦

¦ байт ¦ ¦

¦ ¦

A0 -------Ў¦-CS ¦

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.