Задания для лабораторных работ по курсу «Схемотехника ЭВМ».

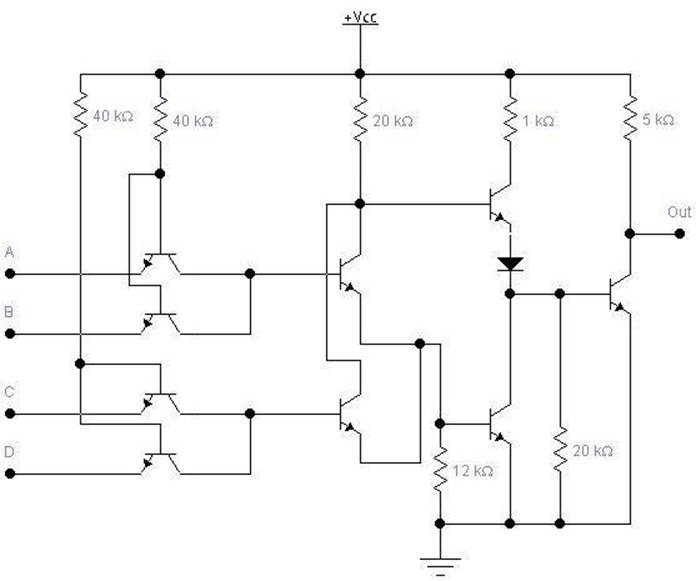

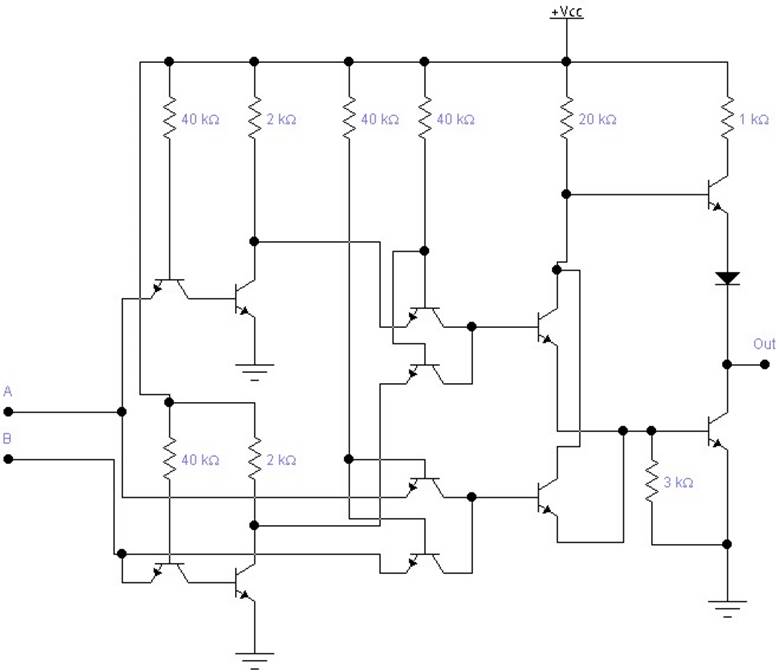

1. Лабораторная работа №1. Моделирование логических элементов на базе ТТЛ.

Задание:

1) ознакомиться с средой моделирования Electronics Workbench v5.12;

2) в указанном программном пакете собрать схему согласно варианту задания;

3) определить логическую операцию, выполняемую схемой, используя прибор «логический преобразователь» (Logic converter). Для этого внести прибор в схему и подключить его клеммы следующим образом:

a. клемму «выход» (Out) к выходу схемы;

b. клеммы A и B (крайние слева на значке прибора) ко входам схемы соответственно;

После этого двойным щелчком по значку прибора вывести на экран панель прибора и щелкнуть по кружкам A и B вверху панели, активировав таким образом эти два канала. Далее получить таблицу истинности функционирования схемы, щелкнув по самой верхней кнопке в группе «преобразования» (conversions). После того, как таблица истинности получена, получить булево выражение для функции, выполняемой схемой или его же в минимизированной форме, нажав соответственно вторую или третью сверху кнопки в группе. Получить эквивалентную схему для выражения в базисе И-НЕ (нижняя в группе conversions кнопка на панели прибора);

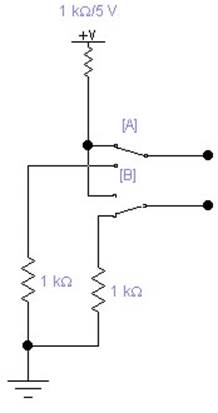

4) определить уровни напряжения логической «1» и логического «0», выдаваемые схемой. Для этого подключить к выходу схемы вольтметр и симулировать работу схемы, изменяя состояния входов, собрав вспомогательную схему на механических ключах и резисторах, как показано на рисунке (переключать ключи можно нажатием клавиш, указанных в квадратных скобках):

5) измерить ток, потребляемый схемой в разных режимах (их не более 4), подключив к ней амперметр (ammeter, панель Indicators). При этом постараться подключить прибор так, чтобы не учитывался ток, потребляемый вспомогательными приборами, используемыми для управления входами схемы;

6) оформить отчет и защитить его. При подготовке к защите настоятельно рекомендуется повторить материал по теме ТТЛ предмета «Схемотехника» за второй курс. Студенты, не представляющие себе работу транзисторного ключа, к защите допускаться просто не будут.

Содержание отчета:

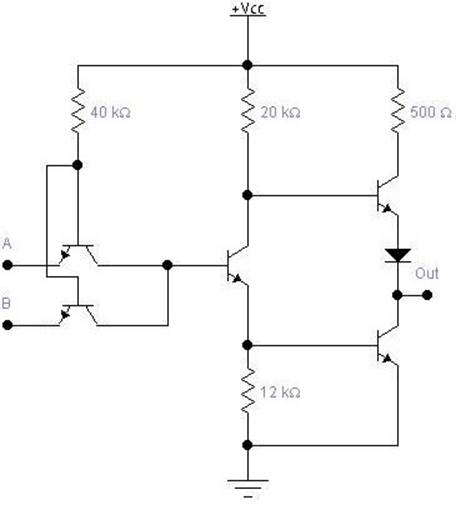

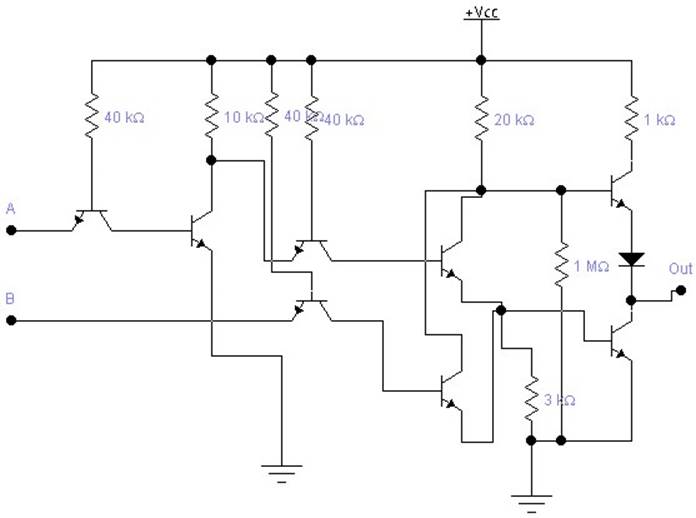

1) исходная схема;

2) таблица истинности схемы и минимизированное булево выражение логической функции, выполняемой схемой;

3) эквивалентная схема в базисе логических элементов И-НЕ;

4) значения напряжений лог. «0» и лог. «1» на выходе схемы;

5) минимальное и максимальное значения тока, потребляемого схемой.

Варианты заданий:

I

V

2. Лабораторная работа №2. Изучение устройств комбинационной логики.

Задание:

1) согласно варианту задания синтезировать комбинационную схему в произвольном базисе и собрать ее в среде моделирования Electronics Workbench;

2) собрать вспомогательные схемы для формирования различных наборов входных сигналов и для индикации результата. Состав и устройство схем - на Ваше усмотрение;

3) промоделировать схему и убедиться в правильности ее функционирования;

4) подключить ко всем входам и выходам исследуемой схемы логический анализатор и получить временные диаграммы функционирования схемы. Показать схему преподавателю;

5) оформить и защитить отчет.

Содержание отчета:

1) Ф.И.О. студентов в бригаде и их группа, фамилия преподавателя, вариант задания;

2) исходное устройство и его комбинационная схема.

Варианты задания:

I.

Схема контроля/генерации четности. Таблица истинности:

|

Входы |

Выходы |

||||

|

D7..D0: число единиц |

ev |

odd |

EVEN |

ODD |

|

|

четно |

H |

L |

H |

L |

|

|

нечетно |

H |

L |

L |

H |

|

|

четно |

L |

H |

L |

H |

|

|

нечетно |

L |

H |

H |

L |

|

|

X |

H |

H |

L |

L |

|

|

X |

L |

L |

H |

H |

|

II.

Мультиплексор «8 на 1». Входы: D7..D0 – источники; A2..A0 – адрес выбираемого источника; #E – разрешение работы. Выходы: Y – прямое значение мультиплексируемой линии, W – ее инверсное значение.

III.

Дешифратор/демультиплексор «3 на 8». Входы: A2..A0 – адрес выбираемой линии; #G – вход разрешения работы. Выходы: #Q7..#Q0 – инверсные выходы дешифратора/прямые выходы демультиплексора.

IV.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.