D 1 0 1 0 1 1

![]()

![]()

![]()

![]()

![]()

![]() Ñ

0 1 0

1 1 0

Ñ

0 1 0

1 1 0

![]()

Эти элементы построены на МДП- транзисторах с использованием такого их свойства, как высокое входное сопротивление, благодаря чему достаточно просто реализуется динамический принцип хранения информации, применение которого позволяет значительно снизить потребляемую мощность элементов и соответственно устройств, в которых они используются. Созданные на МДП- транзисторах динамические логические элементы обладают способностью сохранять установившееся значение логической функции в течение достаточно продолжительного времени tхр после изменения входных сигналов.

По истечении времени хранения tхр состояние динамического элемента изменяется, т.е. хранившаяся информация теряется. Поэтому необходимо ее периодическое восстановление путем подачи последовательности внешних импульсов с периодом t c < t хр . Эти импульсы одновременно являются синхронизирующими, поэтому устройства на динамических элементах всегда синхронные. В таких устройствах используется несколько сдвинутых по фазе последовательностей синхроимпульсов, причем синхронизация осуществляется путем подключения или отключения питания на соответствующих элементах. При этом элементы потребляют мощность от источника питания только в моменты переключения или восстановления информации. Поэтому устройства на динамических элементах потребляют малую мощность на относительно низких частотах переключения. Чаще всего используется двух- или четырехфазная синхронизация.

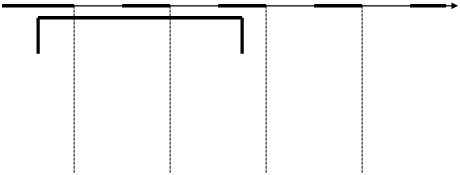

Схема двухфазного динамического элемента и временная диаграмма его работы

![]()

![]()

![]()

![]()

![]() Uип

C

Uип

C

VT2

![]()

![]()

![]()

![]()

![]()

![]() С

С

![]()

![]()

![]()

![]()

![]() C C

C C

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() D

Q

D

Q

![]() VT3

не

VT3

не

Q

![]()

![]()

![]()

![]()

![]() VT1

VT1

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() CЗ1 C З2

CЗ1 C З2

![]() D

D

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

UC

|

UD

UA

![]()

![]() UQ

UQ

t

При возрастании потенциала на входе D выше порога срабатывания транзистора VT1 он открывается и емкость CЗ1 разряжается потенциала @ 0. При поступлении синхроимпульса C1 открываются транзисторы VT2 и VT3, и емкость CЗ2 также разряжается, и на выходе элемента таким образом устанавливается потенциал "0". По окончании импульса C1 транзисторы VT2, VT3 запираются, и заряд на емкости CЗ2 и на выходе Q @ 0 сохраняются в течение времени t хр , которое определяется временем заряда емкости CЗ2 токами утечки.

tхр @ tЗ = RУ CЗ2 , где RУ - сопротивление утечки

При типовых значениях RУ = 108 - 109 и CЗ2 = 0,1 - 1 пф значение t З = 10 - 100 мкс.

Чтобы не произошло потери информации, т.е. ложного срабатывания элемента в состояние "1", необходимо подать новый синхроимпульс раньше, чем потенциал U вых возрастет до потенциала срабатывания элемента нагрузки. При подаче нового синхроимпульса емкость CЗ2 снова разрядится до U0. При снижении входного сигнала до уровня U0 транзистор VT1 закрывается, а при поступлении очередного синхроимпульса открываются VT2, VT3, и емкость CЗ2 заряжается до потенциала U1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.