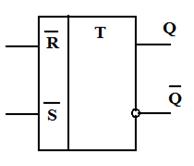

Рис. 4.7

По схеме рис.4.6 не

трудно убедиться, что подача на входы триггера рис.4.6 двух нулей приводит к

неалгоритмическому состоянию триггера ![]() . Такой

режим иногда оказывается целесообразным.

. Такой

режим иногда оказывается целесообразным.

Сложный ТТЛ инвертор в триггерных схемах обычно не используется. Использование ТТЛ логики с увеличенным числом входов может быть полезно в логических операциях, например, при адресном выборе ячеек памяти. Необходимые параметры сигналов переключения триггеров на элементах И-НЕ определяются так же, как показано в 4.5. Полезно самостоятельно построить диаграммы, подобные рис.4.5.

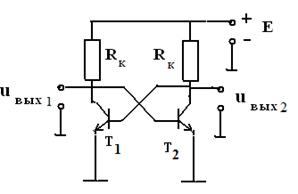

4.7. Триггеры с непосредственными связями

Наиболее массовое и

унифицированное применение триггерных схем имеет место при построении устройств

цифровой памяти. В таком применении важнейшим показателем является плотность

компановки, определяемая числом схем триггеров на единице площади микросхемы.

Для повышения этого показателя следует сокращать число элементов схемы

триггера. Наиболее подходящей для этого является бистабильная ячейка (рис.4.1),

использующая два транзистора и два резистора. Схема такого триггера показана на

рис.4.8. Регенеративный процесс переключения схемы с непосредственными связями

(![]() ), рассмотренный в 4.4 , протекает с

максимальной скоростью, т.к. базовый ток определяется полным изменением

коллекторного тока.

), рассмотренный в 4.4 , протекает с

максимальной скоростью, т.к. базовый ток определяется полным изменением

коллекторного тока.

Рис. 4.8

Логический перепад

при переключении триггера (разность напряжений на коллекторах закрытого и

насыщенного транзисторов) невелик. Например, если в схеме рис.4.8. транзистор ![]() насыщен, то напряжение

насыщен, то напряжение ![]() В, что меньше напряжения

В, что меньше напряжения ![]() , поэтому

, поэтому ![]() закрыт.

Напряжение на коллекторе

закрыт.

Напряжение на коллекторе ![]() при непосредственной

связи равно напряжению на базе открытого (насыщенного) транзистора

при непосредственной

связи равно напряжению на базе открытого (насыщенного) транзистора ![]() :

: ![]() В. Следовательно

логический перепад при переключении триггера с непосредственными связями

составляет

В. Следовательно

логический перепад при переключении триггера с непосредственными связями

составляет ![]() В вне зависимости от напряжения питания.

Это определяет возможность использования напряжений

В вне зависимости от напряжения питания.

Это определяет возможность использования напряжений ![]() около

1 В с соответствующим снижением тепловых потерь, что в свою очередь

способствует достижению более высокой плотности компановки схем памяти. Кроме

того, степень насыщения открытого транзистора триггера с непосредственной

связью довольно высокая:

около

1 В с соответствующим снижением тепловых потерь, что в свою очередь

способствует достижению более высокой плотности компановки схем памяти. Кроме

того, степень насыщения открытого транзистора триггера с непосредственной

связью довольно высокая:

. (4.9)

. (4.9)

Уменьшение напряжения питания

позволяет снизить степень насыщения до приемлемых величин. Например, при ![]() В из (4.9) получаем

В из (4.9) получаем ![]() .

.

Для будущего отметим, что триггерные ячейки типа рис.4.8 являются элементами запоминающих устройств с произвольным доступом, или оперативных запоминающих устройств (ОЗУ), что подразумевает возможность записи данных в ячейку и их считывания (англ. RAM- random access memory). При этом цепи считывания и записи, присоединяемые к выходам 1 и 2 схемы рис.4.8, являются общими для всего запоминающего устройства. Дополнительно используются цепи адресной выборки единственной ячейки, с которой на данном интервале времени осуществляется обмен данными.

4.8. Триггеры со счётным входом

Одна из типичных прикладных задач состоит в определении числа импульсов, приходящих на вход некоторого устройства. Эти импульсы предполагаются одинаковыми по форме и параметрам, в противном случае используются схемы приведения их к идентичному виду. Способ подсчёта числа идентичных импульсов состоит в подаче их на триггер, переключающийся при каждом поступающем импульсе. Это элементарный счётчик, возвращающийся в исходное состояние после двух поданных импульсов. Подсчёт большего количества импульсов потребует построения цепочки триггеров для подсчёта числа переключений первого и последующих триггеров.

Исходя из сказанного, базовым элементом счётчика является триггер с единственным (общим, счётным) входом, последовательная подача на который идентичных импульсов приводит к повторным переключениям триггера. Рассмотренные примеры триггеров переключались идентичными воздействиями, но подаваемыми на различные входы триггера. Следовательно, для построения схемы счётного триггера требуется предусмотреть схему переключения воздействия с общего, счётного входа на входы, ответственные за переключение триггера в противоположные состояния.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.