Хабаровский государственный технический университет

Методическое пособие

для студентов специальности 220100

“Вычислительные машины, комплексы, системы и сети”

Хабаровск

2002

Lection 1

Лекция №1

Схемотехника ЭВМ 1 этап. 1930 – 1940 г. первые п/п сборки микросхем, микросхемы большой и малой степени интеграции.

Появление циклов организации – циклов Фон Неймана.

Цикл Фон Неймана:

1) Фаза выборки команды Счётчик команд МП адресует содержимое ячейки памяти, её содержимое выбирается из памяти и помещается в регистр команд МП

2) Код команды поступает с регистра команд в дешифратор команд, где преобразуется в систему управляющих сигналов.

3) Содержимое счётчика команд инкрементируется

4) Фаза выполнения команды go to 1

|

Представление информации |

|||

|

уровень |

КМОП |

ТТЛ |

ЭСЛ |

|

1 |

1,5-15 V |

5 V |

0 V |

|

0 |

0 V |

0 V |

-5,2 V |

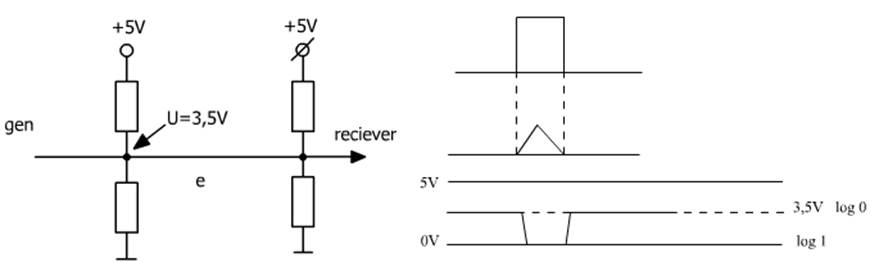

Элементная база – транзисторная логика, для уменьшения задержки при нарастании и спаде уровня сигнала используется пониженное напряжение, уровень 1 примерно 5В.

При работе на высоких частотах при передаче возникает проблема потерь, теряется сигнал в зависимости от волнового сопротивления кабеля или проводника. Применяется эмиттерно-связанная логика. +5В – логический ноль, 0 – логическая единица.

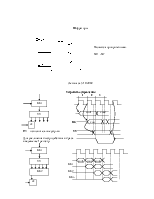

Двухразрядный сумматор

A B Y C’ C C -переход на второй (старший) разряд 00 00 00 0 0 C’ -переполнение сумматора переход на третий разряд 01 00 01 0 0 A -первое двухразрядное число 10 00 10 0 0 B -второе двухразрядное число 11 00 11 0 0 Y -результат суммирования …………………………… 01 01 10 1 0 11 01 00 1 1 11 11 10 1 1

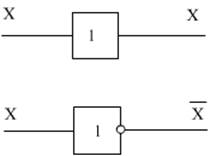

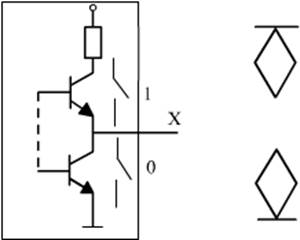

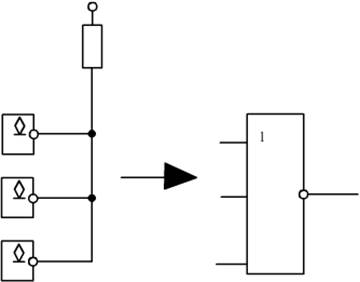

Все логические элементы обладают предельной нагрузочной способностью, т.е. к выходу логического элемента можно подключить строго определённое число входов других элементов.

Данные элементы обладают повышенной нагрузочной

способностью.

Данные элементы обладают повышенной нагрузочной

способностью.

элемент с открытым эмиттером – отсутствует верхний транзистор, (элемент может

подать только 0).

элемент с открытым коллектором – отсутствует нижний транзистор, (элемент может

подать только 1).

пример аналогов

Существуют также элементы, у которых помимо двух основных состояний есть ещё и третье, когда оба транзистора выключены. Все канальные приемо-передатчики обладают возможностью перевода в данное состояние.

Лекция №2

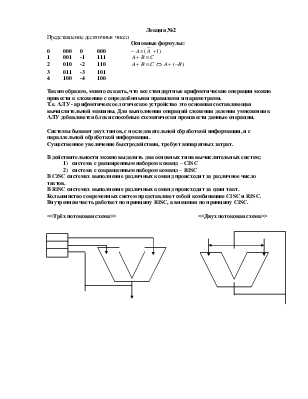

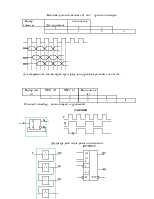

Представление десятичных чисел

Основные формулы:

0 000 0 000 ![]() =(

=(![]()

![]() )

1 001 -1 111

)

1 001 -1 111 ![]()

2 010 -2 110 ![]()

3 011 -3 101

4 100 -4 100

Таким образом, можно сказать, что все стандартные арифметические операции можно привести к сложению с определёнными правилами и параметрами.

Т.е. АЛУ - арифметическое логическое устройство это основная составляющая вычислительной машины. Для выполнения операций сложения деления умножения к АЛУ добавляются блоки способные схематически произвести данные операции. Системы бывают двух типов, с последовательной обработкой информации, и с параллельной обработкой информации. Существенное увеличение быстродействия, требует аппаратных затрат.

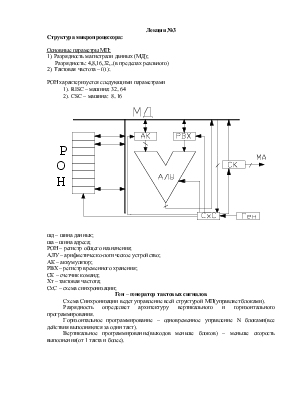

В действительности можно выделить два основных типа вычислительных систем;

1) система с расширенным набором команд – CISC

2) система с сокращенным набором команд – RISC

В CISC системах выполнение различных команд происходит за различное число тактов. В RISC системах выполнение различных команд происходит за один такт.

Большинство современных систем представляют собой комбинацию CISC и RISC. Внутренняя часть работает по принципу RISC, а внешняя по принципу CISC.

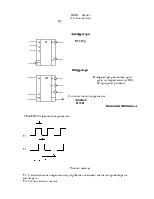

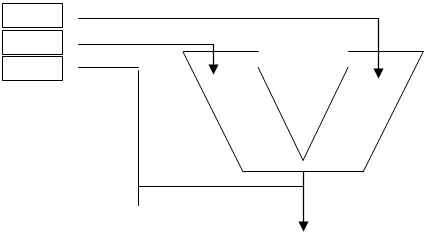

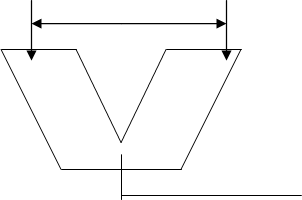

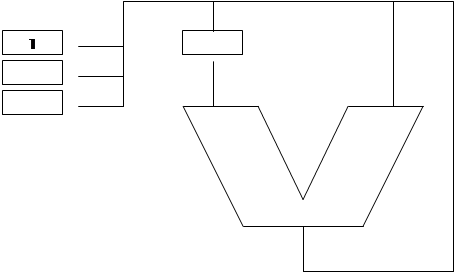

<<Трёх потоковая схема>> <<Двух потоковая схема>>

![]()

![]()

![]()

|

|||

|

|||

<<Аккумуляторный режим работы>>

|

Одно-потоковая структура –Intel организация

Двух потоковая структура – Dec организация

Трех потоковая структура – исп. В супер-ЭВМ

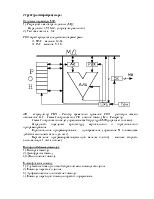

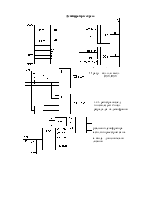

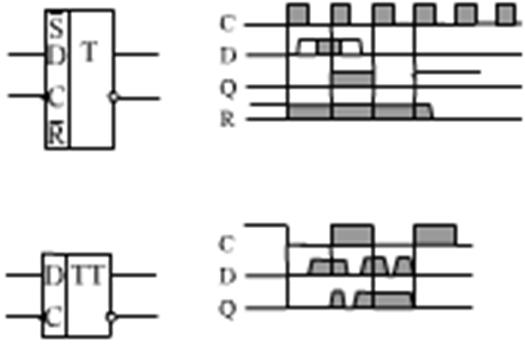

Память на триггерах:

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

С динамической

записью

С статической записью

С динамической

записью

С статической записью

\\Регистр Сумматор + АК

|

![]()

|

|

|

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.