|

|

|

|

|

шд – шина данных;

ша – шина адреса;

РОН – регистр общего назначения;

АЛУ – арифметическо-логическое устройство;

АК – аккумулятор;

РВХ – регистр временного хранения;

СК – счетчик команд;

Хт – тактовая частота;

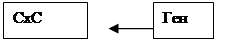

СхС – схема синхронизации;

Ген – генератор тактовых сигналов

Схема 1

Основной параметр, определяющие архитектуру процессора - разрядность шины. Бывают 4, 8, 16, 32, 64-разрядные шины.

РОН (регистр общего назначения) в различных машинах:

3) в RISK машинах размер РОН от 32 до 64

4) в CISK машинах от 8 до 16 (т.н. регистровые машины)

|

|

|

|

Схема 2. Структура горизонтального программирования

Разрядность определяет архитектура вертикального и горизонтального программирования.

Структура горизонтального программирования - почти все действия выполняются в один такт; структура вертикального программирования – в несколько тактов.

3-4. выполнение самой команды

1) служебные команды (общий сброс системы, останов системы, команда ожидания)

2) команды пересылки данных

3) арифметические и логические команды

4) команды переходов

Самый простой и эффективные метод – линейное программирование, когда все команды расположены последовательно. Для организации такой структуры необходимо иметь счетчик.

Разрядность счетчика команд определяет разрядность шины адреса.

|

|

|

|

|||||||||||||||

|

|

||||||||||||||

|

|

|

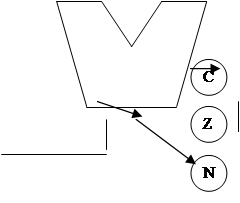

ССП – слово состояния процессора;

C – знак переноса;

Z – признак нуля;

N - знак.

|

|

|

Для каждой из фирм изготовителей стартовый адрес регламентируется.

Самый простой вариант – система стартует по нулевому адресу.

1 группа команд. Все 8 разрядов - чтение кода команды.

![]()

2 группа команд. Несколько старших разрядов отвечают за код операции, остальные несут информацию об источниках данных.

|

|

DEC’овская архитектура - 16-разрядные команды.

![]() адрес источника

адрес источника

![]() 01 02 04

01 02 04

адрес приемника

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

|

|

DEC’овская архитектура - внутренняя 2-х шинная архитектура.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.