DEC’овская архитектура - внутренняя 2-х шинная архитектура.

8 РОН

8 методов адресации всего по 8.

2 группа команд:

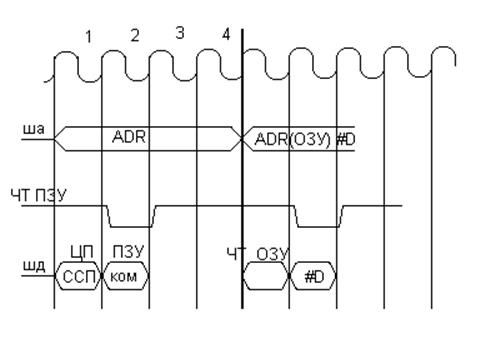

Команда занимает несколько тактов (минимум 3) и может занимать несколько циклов.

14.09.

Представление информации:

- Символическое:

|

уровень «0» - 0 В.

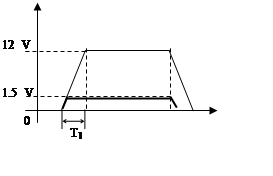

- Транзисторная логика (ТТЛ):

«1» - 5 В.

«0» - 0 В.

- Эмиттерно-связанная логика (ЭСЛ):

Связь осуществляется через эмиттерный переход.

Отрицательное смещение:

«1» - 0 В.

«0» - 5,2 В.

Представление информации по логическим уровням:

- уровень «1»

|

информация не передается:

|

||

|

Одноразрядный сумматор.

Одноразрядный сумматор.

|

х1 |

х2 |

Y |

С |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

C – перенос.

Двухразрядный сумматор.

|

A |

B |

Y |

C’ |

C |

|

00 |

00 |

00 |

0 |

0 |

|

01 |

00 |

01 |

0 |

0 |

|

10 |

00 |

10 |

0 |

0 |

|

11 |

00 |

11 |

0 |

0 |

|

00 |

01 |

01 |

0 |

0 |

|

01 |

01 |

10 |

1 |

0 |

|

10 |

01 |

11 |

0 |

0 |

|

11 |

01 |

00 |

1 |

1 |

|

00 |

10 |

10 |

0 |

0 |

|

01 |

10 |

11 |

0 |

0 |

|

10 |

10 |

00 |

0 |

1 |

|

11 |

10 |

01 |

0 |

1 |

|

00 |

11 |

11 |

0 |

0 |

|

01 |

11 |

00 |

1 |

1 |

|

10 |

11 |

01 |

0 |

1 |

|

11 |

11 |

10 |

1 |

1 |

C – перенос старшего разряда.

С' – перенос младшего разряда.

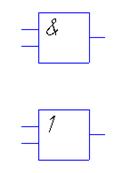

Элементы:

![]()

- повторитель.

Каждый элемент обладает свойствами:

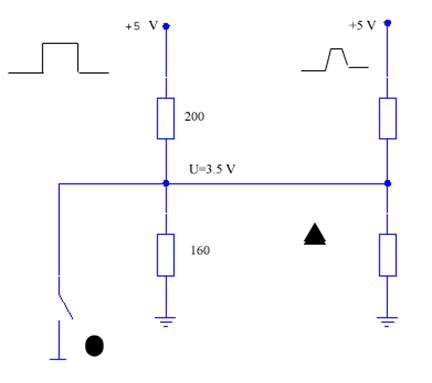

-к одному выходу элемента ограниченное число

входов – нагрузочная способность.

-к одному выходу элемента ограниченное число

входов – нагрузочная способность.

-повышение нагрузочной способности до 25 В.

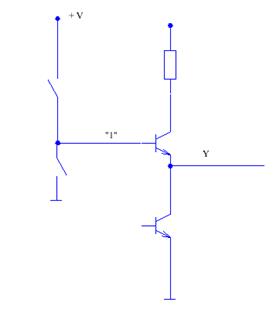

-элемент с открытым коллектором.

![]()

![]()

![]()

![]() - элемент с открытым коллектором,

отсутствие верхнего транзистора (нужно подавать 0).

- элемент с открытым коллектором,

отсутствие верхнего транзистора (нужно подавать 0).

если:

![]() - элемент с открытым

коллектором, отсутствует нижний транзистор (нужно подавать 1).

- элемент с открытым

коллектором, отсутствует нижний транзистор (нужно подавать 1).

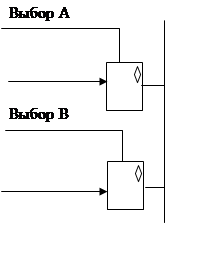

![]() - элемент с 3

состояниями: на выходе возможно 3 состояния:

- элемент с 3

состояниями: на выходе возможно 3 состояния: ![]() - 0;

- 0; ![]() - 1; отключенный.

- 1; отключенный.

включает либо А или В.

Все каналы прямые передатчики, обладающие возможностью перехода этих состояний.

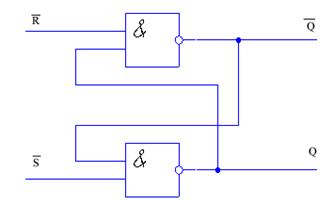

RS – триггер.

RS – триггер.

21.09.

Представление целых чисел.

000 представление отрицательных чисел:

001 111 1).

![]()

010 101– -3 2). +1

![]() 011 -3 100

011 -3 100

.

.

111

первый бит выделяется под знак.

Сложение А + В = С

Вычитание А – В = С = А + (-В)

Умножение ![]() - сдвиг влево:

- сдвиг влево:  ;

;

Деление - сдвиг влево.

|

Арифметически логическое устройство – основной блок процессора.

Микропроцессор:

- операционное устройство – ОУ

- устройство управления – УУ – синхронизация потока данных.

Системы:

- параллельной обработки информации.

- последовательной обработки информации.

|

система последовательной обработки информации.

Любое убыстрение процесса требует увеличение аппаратных затрат, следовательно существует два направления развития ЭВМ.

1. Системы с расширенным набором команд CISC-системы: каждая команда выполняется за определенное количество тактов.

2. Системы с расширенным набором команд RISC-системы: все команды в таких системах выполняются за 1 такт.

Внешне эти системы похожи, но внутри МП различны.

Структура система.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.