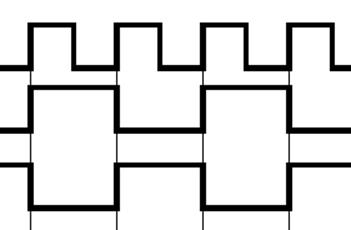

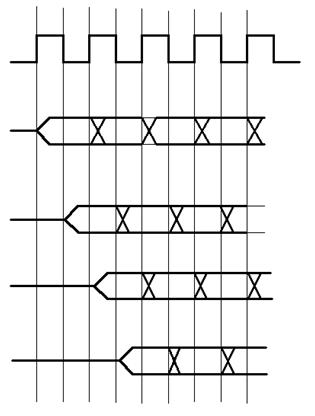

Обычно используется 4-х уровневый конвейер, но есть и больше.

Схемотехника

|

|

||||

|

|||||

C

Q

|

|

Такой шифратор является приоритетным, т. е.

От D0 до D7

Такой шифратор является приоритетным, т. е.

От D0 до D7

Лекция № 4

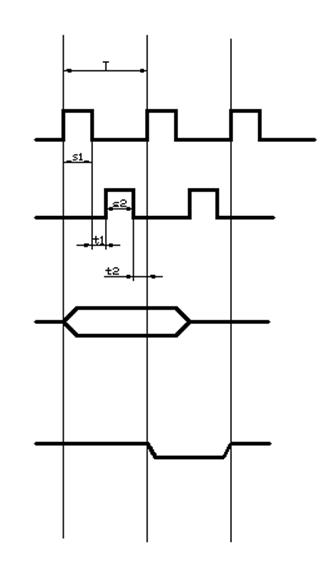

Синхронизация 12 Вольт:

|

s1<s2

Все процессоры - в многофазной синхронизации.

Первые машины Intel 8080:

Чтение команды из ПЗУ:

Т1 – на ШД формируется слово состояние операционного устройства (процессора);

![]() Т2 – формируется сигнал чтения (у

процессора нет отдельных сигналов с регистра или временных устройств);

Т2 – формируется сигнал чтения (у

процессора нет отдельных сигналов с регистра или временных устройств);

Т3

Т4 для дешифрования и выполнения

Т5

Дальше выполняется чтение 2-го байта команды.

|

|

|

|

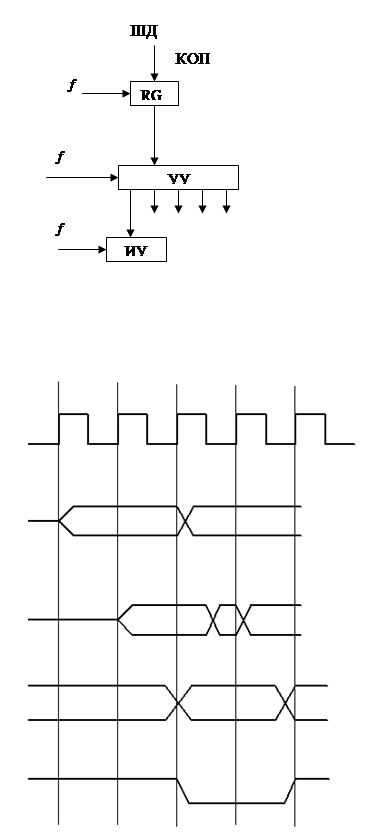

RG

УУ

ИУ

Повышаем быстродействие:

Код операции занимает 1 такт.

|

|||

|

|||

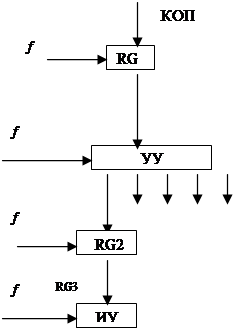

ШД

RG1

RG2

RG3

Получаем принцип конвеера:

i-я команда – выполняется

i+1 команда - выбирается

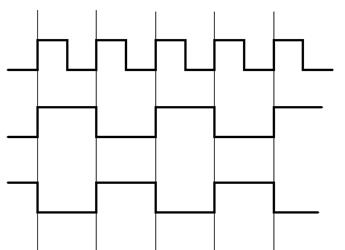

Смещение по времени:

|

Выборка команды |

DEC |

Выполнение |

||

|

Выборка команды |

DEC |

Выполнение |

||

|

Выборка команды |

DEC |

Выполнение |

||

|

ШД

RG1

RG2

RG3

Прекрасно работает при линейном программировании, когда неизвестен адрес следующей команды.

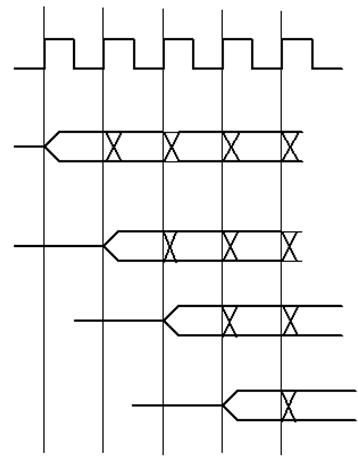

В современных системах используется следующая организация:

|

Выборка команды |

DEC |

DEC |

Выполнение |

||

|

Выборка команды |

DEC |

DEC |

Выполнение |

||

|

Выборка команды |

DEC |

DEC |

Выполнение |

||

|

|

|

|

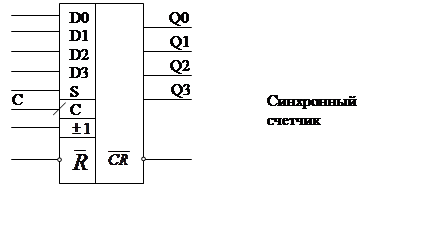

Счетный D-триггер – делит входную частоту на 2.

|

C

Q

_

Q

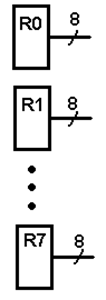

Двоичный последовательный четырехразрядный счетчик:

|

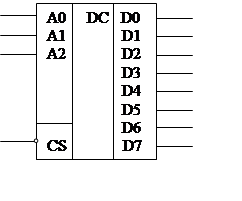

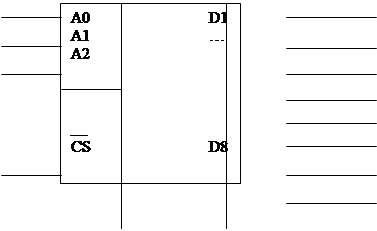

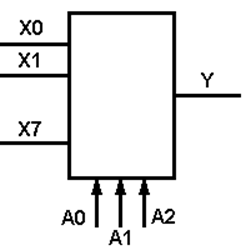

Дешифратор:

|

Самый простой дешифратор – 3 входа – 8 выходов.

|

![]()

![]()

![]()

|

|

||||||||

Шифраторы являются приоритетными (если пришло два сигнала одновременно на D0 и D3, то первым пройдет D0, а потом D3).

Lection 3

12.10.02

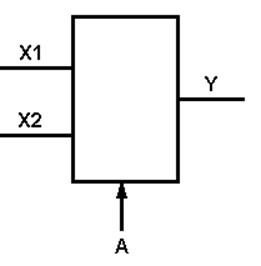

Мультикомплексоры

|

|

A |

X1 |

X2 |

Y |

|

0 |

1/0 |

1/0 |

X1 |

|

1 |

1/0 |

1/0 |

X2 |

|

2:1

4:1

![]() 8:1

8:1

|

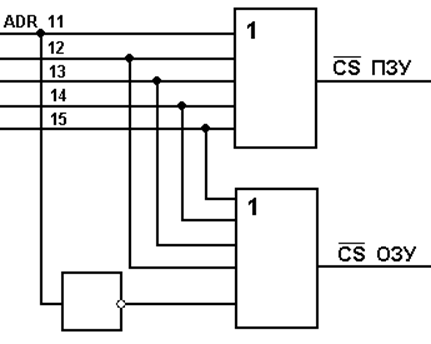

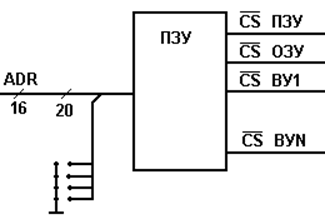

CS – выбор кристалла

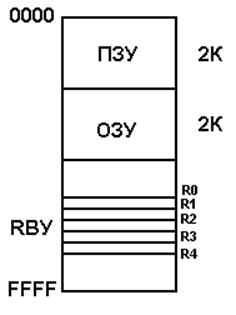

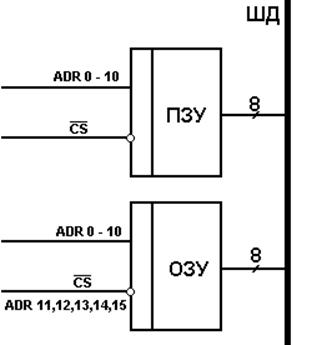

Дешифраторы адреса

если ADR 11-15=0

то работает ПЗУ

11 разр. – вкл. или выкл.

ОЗУ, ПЗУ

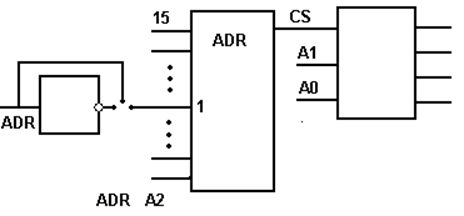

т.к. 4 регистра послед.

то используют 2 посл.

разряда для их дешифрации

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.