Y => NET10777

);

U16 : nao3

port map(

A => NET10595,

B => NET10713,

C => X1,

D => NET10634,

Y => Y1

);

Y4 <= NET10713;

Y2 <= NET10744;

Y5 <= NET10777;

U2 : na2

port map(

A => X1,

B => X4,

Y => NET590

);

U3 : no3

port map(

A => X2,

B => X4,

C => NET664,

Y => NET648

);

U4 : N

port map(

A => X1,

Y => NET664

);

U5 : nao22

port map(

A => X4,

B => X1,

C => X2,

D => NET590,

Y => NET735

);

U6 : N

port map(

A => X3,

Y => NET807

);

U7 : no3a2

port map(

A => X3,

B => NET689,

C => X1,

D => X4,

Y => NET714

);

U8 : naoa2

port map(

A => NET807,

B => NET648,

C => NET664,

D => NET10744,

Y => NET10595

);

U9 : no3

port map(

A => NET689,

B => NET807,

C => X4,

Y => NET10713

);

end Schema_own;

2. Составили графическую схему варианта с помощью встроенных элементов.

---------------------------------------------------------------------------------------------------

--

-- Title : No Title

-- Design : nLab_11_design

-- Author : Buffovich

-- Company : Adequatus

--

---------------------------------------------------------------------------------------------------

--

-- File : F:\Workplace Buffovich\Math Models\nLab_11\nLab_11_do\nLab_11_design\compile\Schema_builtin.vhd

-- Generated : Mon May 21 12:39:49 2007

-- From : F:/Workplace Buffovich/Math Models/nLab_11/nLab_11_do/nLab_11_design/src/Schema_builtin.bde

-- By : Bde2Vhdl ver. 2.6

--

---------------------------------------------------------------------------------------------------

--

-- Description :

--

---------------------------------------------------------------------------------------------------

-- Design unit header --

library IEEE;

use IEEE.std_logic_1164.all;

entity Schema_builtin is

port(

X1 : in STD_LOGIC;

X2 : in STD_LOGIC;

X3 : in STD_LOGIC;

X4 : in STD_LOGIC;

Y1 : out STD_LOGIC;

Y2 : out STD_LOGIC;

Y3 : out STD_LOGIC;

Y4 : out STD_LOGIC;

Y5 : out STD_LOGIC

);

end Schema_builtin;

architecture Schema_builtin of Schema_builtin is

---- Constants -----

constant GND_CONSTANT : STD_LOGIC := '0';

---- Signal declarations used on the diagram ----

signal GND : STD_LOGIC;

signal NET103 : STD_LOGIC;

signal NET107 : STD_LOGIC;

signal NET117 : STD_LOGIC;

signal NET124 : STD_LOGIC;

signal NET132 : STD_LOGIC;

signal NET172 : STD_LOGIC;

signal NET286 : STD_LOGIC;

signal NET302 : STD_LOGIC;

signal NET310 : STD_LOGIC;

signal NET398 : STD_LOGIC;

signal NET415 : STD_LOGIC;

signal NET418 : STD_LOGIC;

signal NET445 : STD_LOGIC;

signal NET517 : STD_LOGIC;

signal NET529 : STD_LOGIC;

signal NET766 : STD_LOGIC;

signal NET794 : STD_LOGIC;

signal NET802 : STD_LOGIC;

signal NET826 : STD_LOGIC;

signal NET83 : STD_LOGIC;

signal NET87 : STD_LOGIC;

signal NET926 : STD_LOGIC;

signal NET927 : STD_LOGIC;

signal NET928 : STD_LOGIC;

begin

---- Component instantiations ----

NET415 <= not(X1);

NET302 <= X4 and X1;

NET103 <= NET418 and NET415;

NET802 <= not(NET107 and NET445);

NET107 <= NET103 or NET398;

NET926 <= not(X4 or NET445 or X3);

NET766 <= not(X4);

NET117 <= NET529 and X3;

NET794 <= not(NET117 or NET517);

NET826 <= not(NET928);

NET124 <= NET415 or NET445;

NET310 <= not(X2);

NET132 <= NET124 and X2;

NET418 <= not(NET132 or NET766);

NET928 <= not(NET794);

NET927 <= not(NET172 and NET802);

NET172 <= NET826 or X1 or NET926;

Y1 <= NET927;

Y2 <= NET418;

Y3 <= GND;

Y4 <= NET926;

Y5 <= NET928;

NET286 <= not(X4 and X1);

NET398 <= not(NET415 or X4 or X2);

NET83 <= X1 or X4;

NET87 <= NET286 or X2;

NET529 <= not(NET87 and NET83);

NET445 <= not(X3);

NET517 <= not(NET302 or NET310 or X3);

---- Power , ground assignment ----

GND <= GND_CONSTANT;

end Schema_builtin;

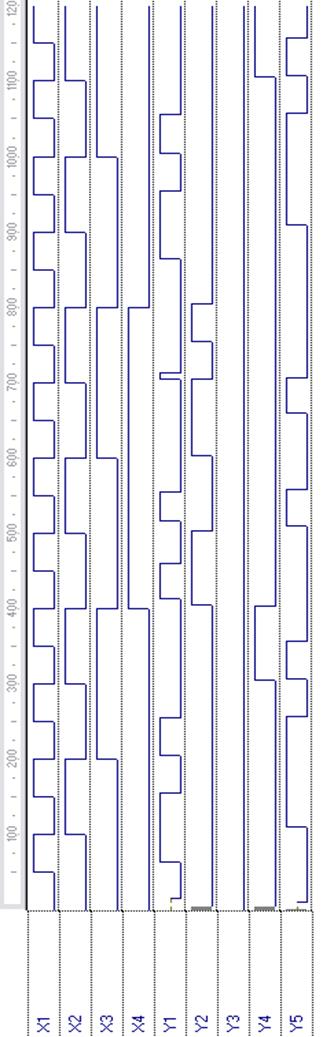

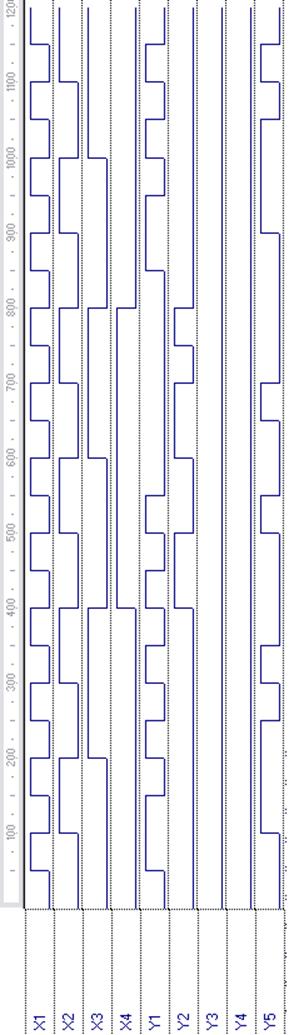

3. Составили схему тестирующих воздействий и выполнили моделирование.

Вывод: Были изучены возможности языка VHDL и пакета ActiveHDL для проектирования заказных БИС.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.