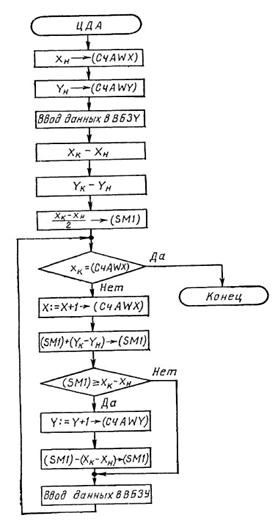

Следовательно, блок-схему

алгоритма рис. 2.11 надо дополнить операцией проверки условия ![]() , в зависимости от выполнения которого

осуществляется выбор уравнения (2.32) или (2.35) (

, в зависимости от выполнения которого

осуществляется выбор уравнения (2.32) или (2.35) (![]() обозначает

знак результата в круглых скобках). Кроме того, необходимо также проверить

значения функций

обозначает

знак результата в круглых скобках). Кроме того, необходимо также проверить

значения функций ![]() и

и ![]() ,

которые определяют направления приращения координат

,

которые определяют направления приращения координат ![]() и

и

![]() . При положительном значении указанных

функций адресные счетчики работают в режиме суммирования, а при отрицательном

знаке – в режиме вычитания.

. При положительном значении указанных

функций адресные счетчики работают в режиме суммирования, а при отрицательном

знаке – в режиме вычитания.

|

Рис. 2.11. Блок-схема алгоритма работы генератора векторов, работающего

по принципу цифрового дифференциального анализатора:

SM – сумматор; Сч AWX; AWY – счетчики адреса записи

|

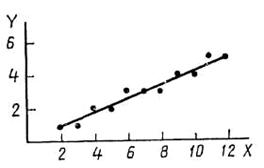

Рис. 2.12. Аппроксимация отрезка прямой точечными ЭО

Задание 2.7. Составить структурную схему устройства формирования вертикального отклонения для буквенно-цифрового СОИ с 7-сегментной полиграммой. Система отклонения электронного луча – электростатическая.

В устройство формирования

напряжения входит преобразователь кодов ПК Y, цифроаналоговый преобразователь ЦАП Y и усилитель вертикального отклонения.

В соответствии с выражениями (2.32)  , определяем

разрядность счетчика сегментов и входов ПК Х и ПК Y. Число сегментов, включая сегменты,

формируемые при повторном прохождении луча,

, определяем

разрядность счетчика сегментов и входов ПК Х и ПК Y. Число сегментов, включая сегменты,

формируемые при повторном прохождении луча, ![]() .

Для указанной полиграммы

.

Для указанной полиграммы ![]() ;

; ![]() . Следовательно,

. Следовательно, ![]() ;

; ![]() ;

; ![]() .

.

В соответствии с диаграммой рис. 2.14 составим таблицу истинности для преобразователей ПК Y.

Низкому уровню сигнала Y соответствует ![]() ,

,

![]() ; среднему −

; среднему − ![]() ;

высокому −

;

высокому − ![]() ,

, ![]() .

Уровни изменяются в начале формирования очередного СП. Минимизируя логические

функции

.

Уровни изменяются в начале формирования очередного СП. Минимизируя логические

функции ![]() и

и ![]() ,

получаем

,

получаем ![]() ,

, ![]() .

Эти выражения могут быть реализованы на базе комбинированных логических схем.

Более простую их реализацию можно получить, используя мультиплексоры. На

адресные входы мультиплексора подается комбинация сигналов

.

Эти выражения могут быть реализованы на базе комбинированных логических схем.

Более простую их реализацию можно получить, используя мультиплексоры. На

адресные входы мультиплексора подается комбинация сигналов ![]() , а на его информационные входы –

логическая единица или ноль в соответствии с табл. 2.2. Полученная схема

преобразователя показана на рис. 2.16.

, а на его информационные входы –

логическая единица или ноль в соответствии с табл. 2.2. Полученная схема

преобразователя показана на рис. 2.16.

Преобразование

кода ![]() ;

; ![]() в три уровня осуществляется простейшим

цифроаналоговым преобразователем на базе резистивного

делителя

напряжения к ключей на транзисторах;

в три уровня осуществляется простейшим

цифроаналоговым преобразователем на базе резистивного

делителя

напряжения к ключей на транзисторах; ![]() ;

;

![]() . Включение

. Включение ![]() и

и

![]() обеспечивает наименьший коэффициент передачи, включение

обеспечивает наименьший коэффициент передачи, включение ![]() − средний; включение

− средний; включение ![]() −

высокий. В качестве интегрирующей цепочки используется простейший

−

высокий. В качестве интегрирующей цепочки используется простейший ![]() -фильтр, с выхода которого снимается сигнал

-фильтр, с выхода которого снимается сигнал ![]() .

.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.