2. Выбираем

в качестве ОЗУ Нк БИС, имеющую информационную емкость ![]() и максимальное

время выборки относительно адреса

и максимальное

время выборки относительно адреса ![]() нс.

нс.

3. По формуле (2.4) ![]() находим длительность импульса,

формирующего ЭО:

находим длительность импульса,

формирующего ЭО: ![]() нс.

нс.

4. Рассчитываем

коэффициент увеличения разрядности ВБЗУ при чтении по

формуле (3.17) ![]() (зададимся значением

(зададимся значением ![]() нс):

нс): ![]() .

Выбираем

.

Выбираем ![]() .

.

5. Определяем

разрядность ВБЗУ при чтении ![]() .

.

6. Находим значение ![]() по

формуле (3.20):

по

формуле (3.20): ![]() ;

; ![]() ,

число рядов

,

число рядов ![]() − по формуле (3.21)

− по формуле (3.21) ![]() , найдя предварительно

по формуле (3.19)

, найдя предварительно

по формуле (3.19) ![]() число

ячеек памяти ВБЗУ:

число

ячеек памяти ВБЗУ: ![]() K;

K; ![]() .

.

7. Определяем

период регенерации памяти по формуле (3.22) ![]() ;

;

![]() мкс, что полностью удовлетворяет требованиям

технических условии.

мкс, что полностью удовлетворяет требованиям

технических условии.

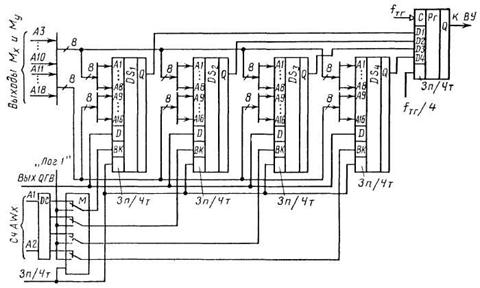

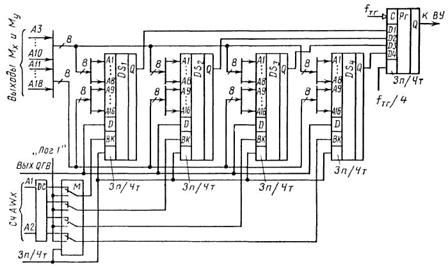

8. На основе полученных результатов построим структурную схему модуля ВБЗУ (рис. 3.4) и рассмотрим ее работу.

В режиме записи модуль ВБЗУ

следует рассматривать как модуль ЗУ с организацией ![]() , четыре БИС которого наращивают

требуемый объем ЗУ (

, четыре БИС которого наращивают

требуемый объем ЗУ (![]() ). Запись

информации происходит поочередно в одноименные ячейки памяти (имеющие

одинаковый адрес) каждой микросхемы. Для этого младшие разряды A1; A2адресного счетчика записи подаются на вход дешифратора, с

помощью которого через мультиплексор М осуществляется выбор одной

из БИС по входам ВK. Остальные

адресные разряды счетчика записи подаются на объединенные адресные

входы БИС. Информационные входы БИС объединены и подключены к информационному

выходу генератора векторов (ГВ).

). Запись

информации происходит поочередно в одноименные ячейки памяти (имеющие

одинаковый адрес) каждой микросхемы. Для этого младшие разряды A1; A2адресного счетчика записи подаются на вход дешифратора, с

помощью которого через мультиплексор М осуществляется выбор одной

из БИС по входам ВK. Остальные

адресные разряды счетчика записи подаются на объединенные адресные

входы БИС. Информационные входы БИС объединены и подключены к информационному

выходу генератора векторов (ГВ).

В режиме

чтения организация ВБЗУ ![]() , что

обеспечивается перестройкой организации

матрицы накопителей, которая в этом случае состоит из одной строки (

, что

обеспечивается перестройкой организации

матрицы накопителей, которая в этом случае состоит из одной строки (![]() ) с четырьмя

микросхемами в строке (

) с четырьмя

микросхемами в строке (![]() ).

).

Изменение организации

матрицы накопителей осуществляется с помощью мультиплексора М. В

режиме записи М обеспечивает подключение ко входам ВK выходов дешифратора

номера ряда матрицы накопителей. На вход дешифратора заведено два младших

адресных разряда, что обеспечивает последовательное

распределение ячеек памяти по разным БИС ОЗУ Нк. В режиме чтения на входы ВK всех микросхем подается логическая единица, что приводит

к увеличению разрядности информационных слов (

Изменение организации

матрицы накопителей осуществляется с помощью мультиплексора М. В

режиме записи М обеспечивает подключение ко входам ВK выходов дешифратора

номера ряда матрицы накопителей. На вход дешифратора заведено два младших

адресных разряда, что обеспечивает последовательное

распределение ячеек памяти по разным БИС ОЗУ Нк. В режиме чтения на входы ВK всех микросхем подается логическая единица, что приводит

к увеличению разрядности информационных слов (![]() ).

На объединенные адресные входы всех БИС подается сигнал oт адресных счетчиков чтения. На каждый четвертый тактовый

импульс происходит перезапись содержимого ячеек памяти в параллельно-последовательный регистр

).

На объединенные адресные входы всех БИС подается сигнал oт адресных счетчиков чтения. На каждый четвертый тактовый

импульс происходит перезапись содержимого ячеек памяти в параллельно-последовательный регистр ![]() ,

с которого информация последовательно

выводится в канал видеоусилителя (ВУ) с частотой

,

с которого информация последовательно

выводится в канал видеоусилителя (ВУ) с частотой ![]() .

.

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.