+ HOLDTIME = 3NS

+ WHEN = { RBAR!='0 & (PEBAR!='1 ^ CHANGED(PEBAR,0)) }

+ SETUP_HOLD:

+ DATA(1) = RBAR

+ CLOCK LH = CLK

+ RELEASETIME_LH = 25NS

*

.ENDS

*

*$

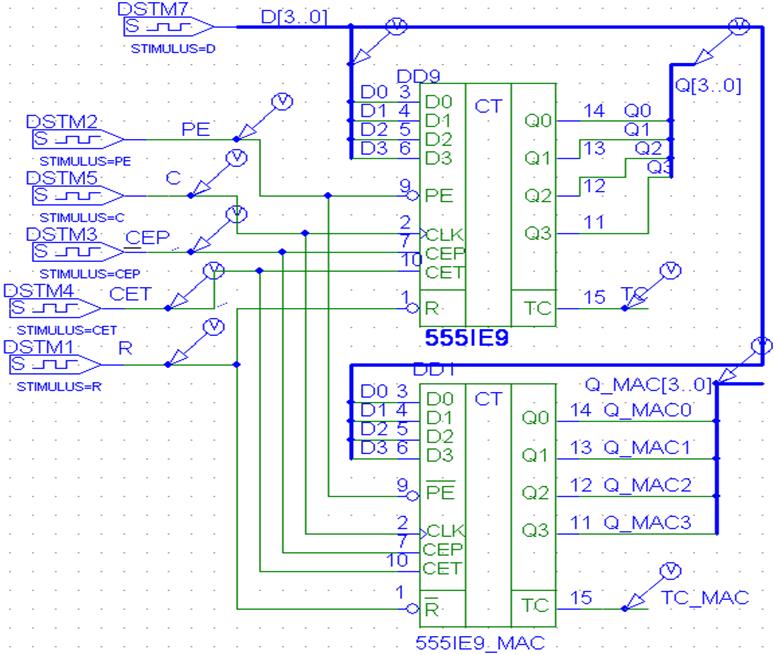

Рис. 14. Схема верификации символа с подключённой к нему макромоделью

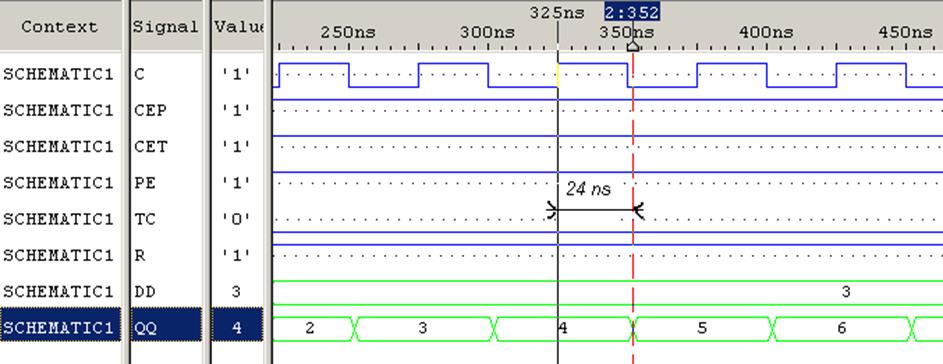

Рис. 15. График из постпроцессора моделирования

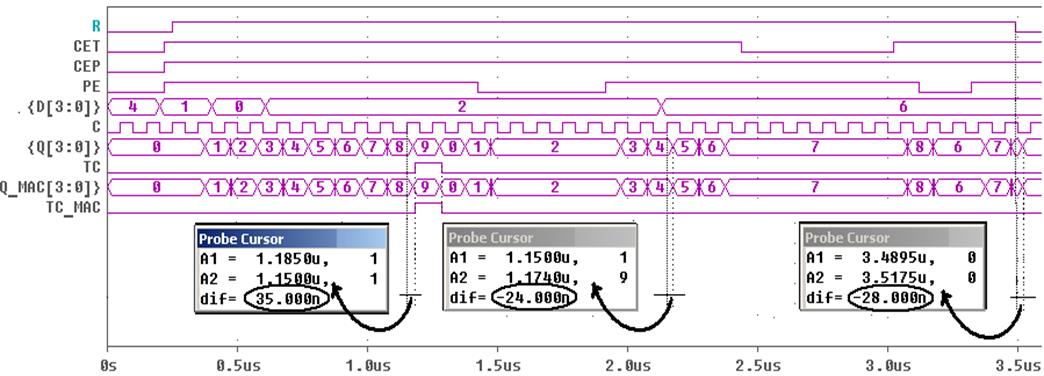

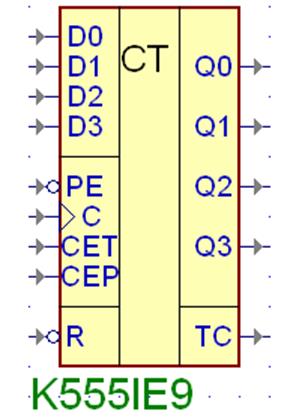

Рис. 16. УГО моделируемого узла

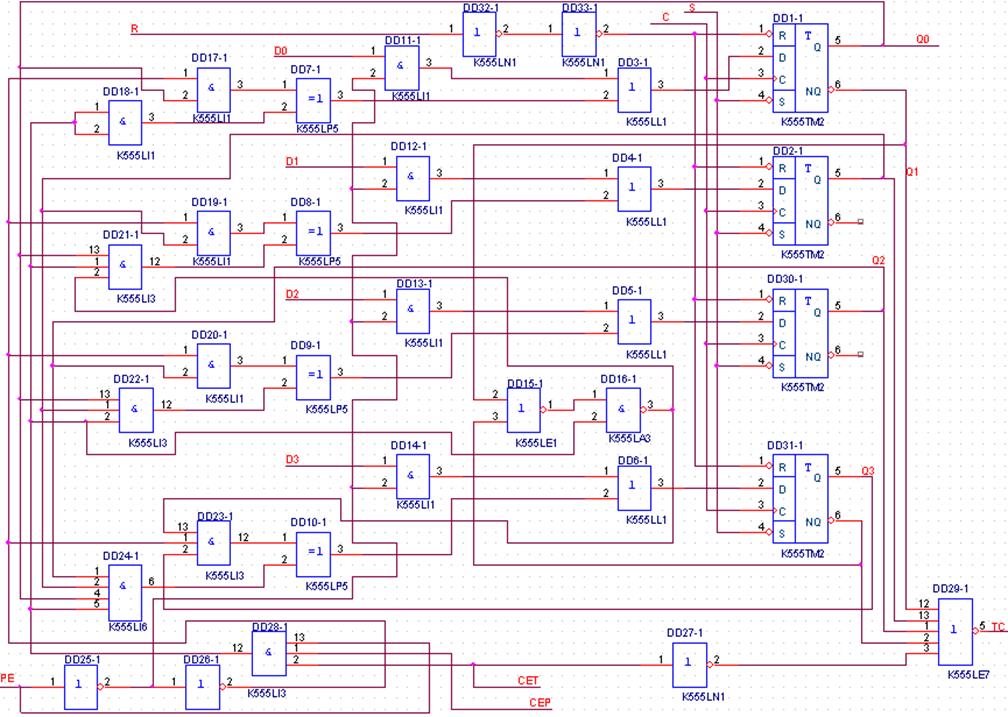

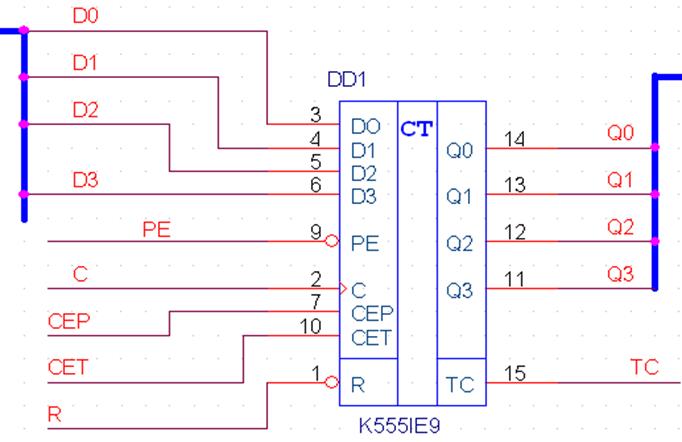

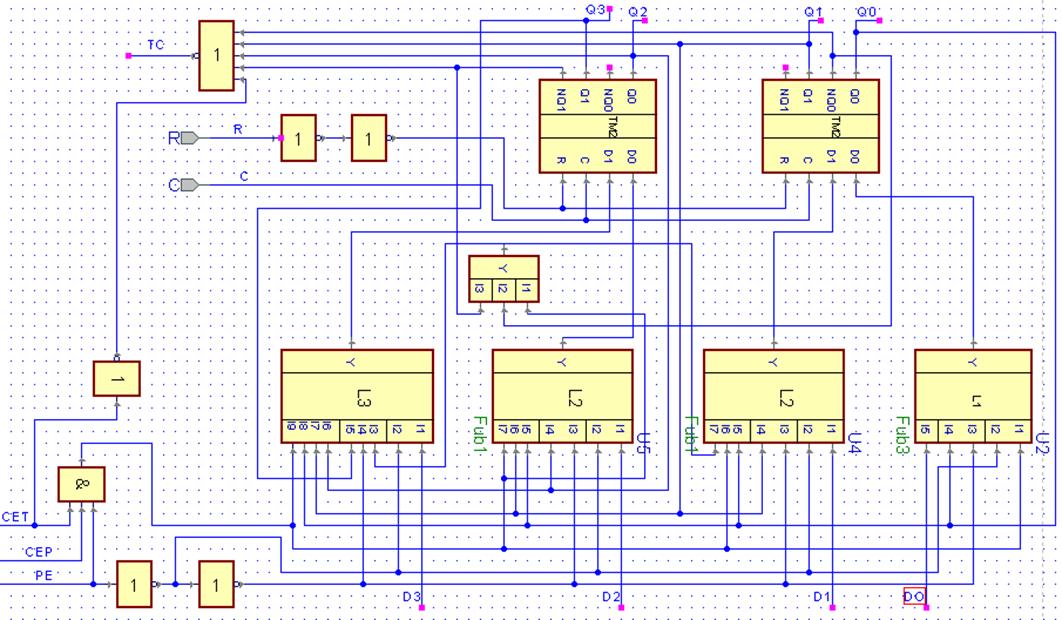

Рис. 17. Принципиальная схема моделируемого узла.

Рис. 18. Схема верификации моделируемого узла

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_SIGNED.all;

entity K555IE9 is

PORT (

D0 : IN std_logic;

D1 : IN std_logic;

D2 : IN std_logic;

D3 : IN std_logic;

Q0 : OUT std_logic;

Q1 : OUT std_logic;

Q2 : OUT std_logic;

Q3 : OUT std_logic;

C, CET,CEP, R, PE,GND,PWR : IN std_logic;

TC: OUT std_logic);

end K555IE9;

architecture MODEL of K555IE9 is

begin

process(PE,R,C,CET,CEP)

variable Q_INT: std_logic_vector (3 downto 0);

variable D_INT: std_logic_vector (3 downto 0);

variable PER_INT: std_logic;

egin

D_INT:=D3&D2&D1&D0;

if R='0' then

Q_INT:="0000";

PER_INT:= '0';

elsif (PE='0') then

Q_INT:=D_INT;

if(D_INT = X"9")then

PER_INT:='1';

end if;

IF(Q_INT > "1001" ) THEN

Q_INT:="0000";

END IF;

elsif (C='1' and C'EVENT AND CET ='1' AND CEP='1') then

if(Q_INT = x"9" )then

Q_INT:="0000";

else

Q_INT:=Q_INT+"0001";

end if;

if(Q_INT = x"9")then

PER_INT:= '1';

else

PER_INT:= '0';

end if;

end if;

IF(Q_INT= X"2" OR Q_INT= X"4" OR Q_INT= X"6" OR Q_INT= X"8")THEN

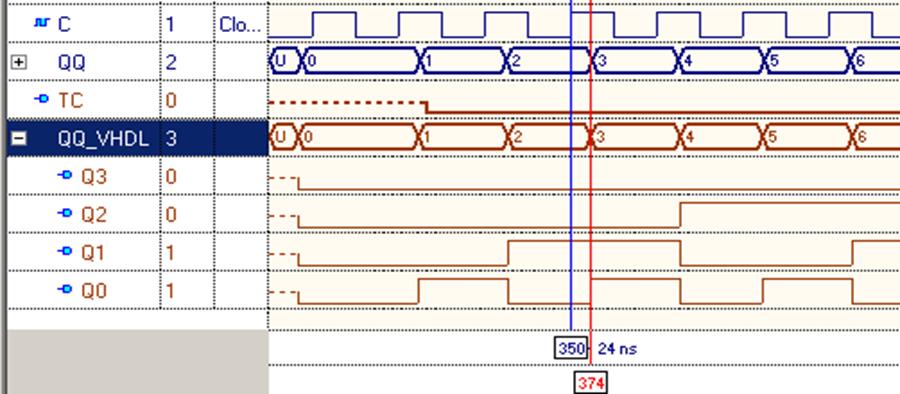

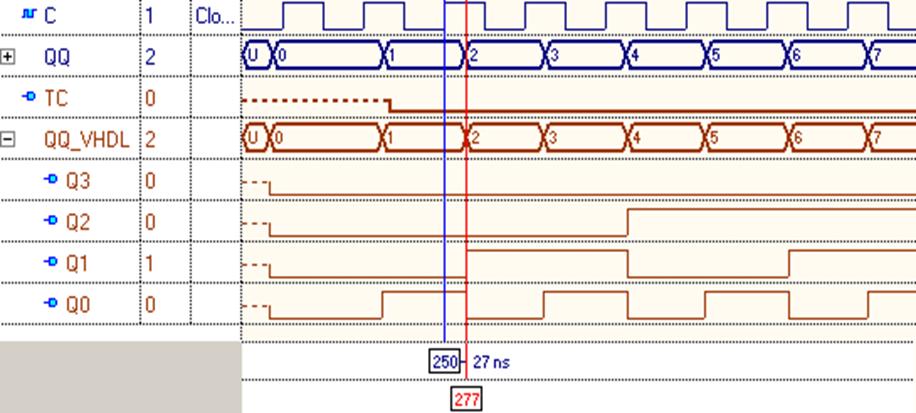

(Q3,Q2,Q1,Q0)<=Q_INT after 27ns;

ELSIF (R='1')then

(Q3,Q2,Q1,Q0)<=Q_INT after 24ns;

elsif (R='0') then

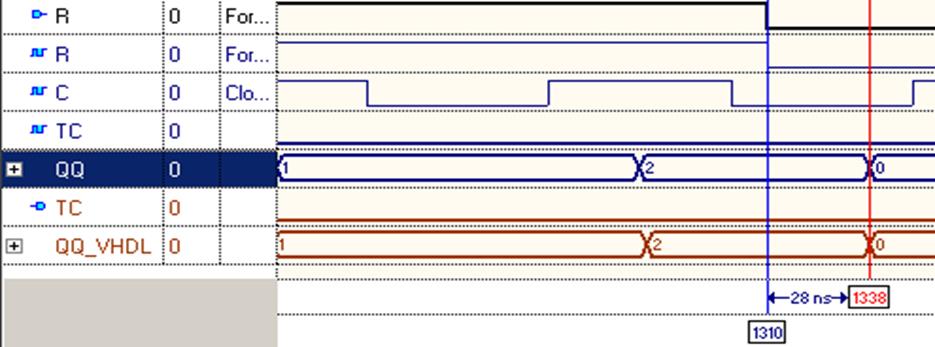

(Q3,Q2,Q1,Q0)<=Q_INT after 28ns;

END IF;

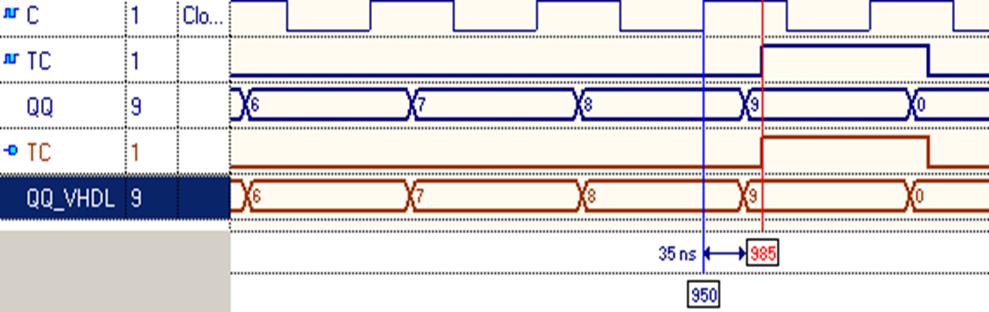

TC<=PER_INT after 35ns;

end process;

end MODEL;

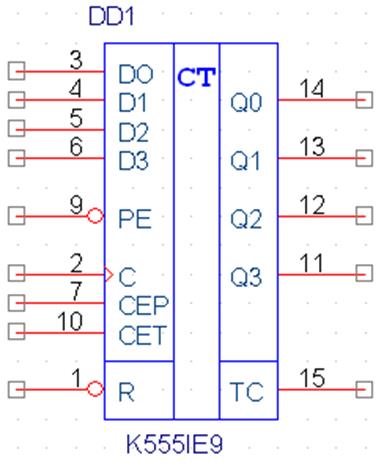

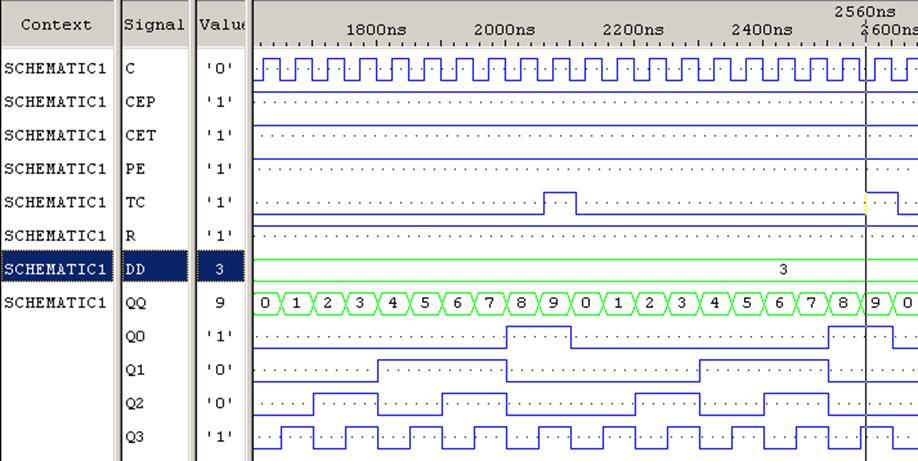

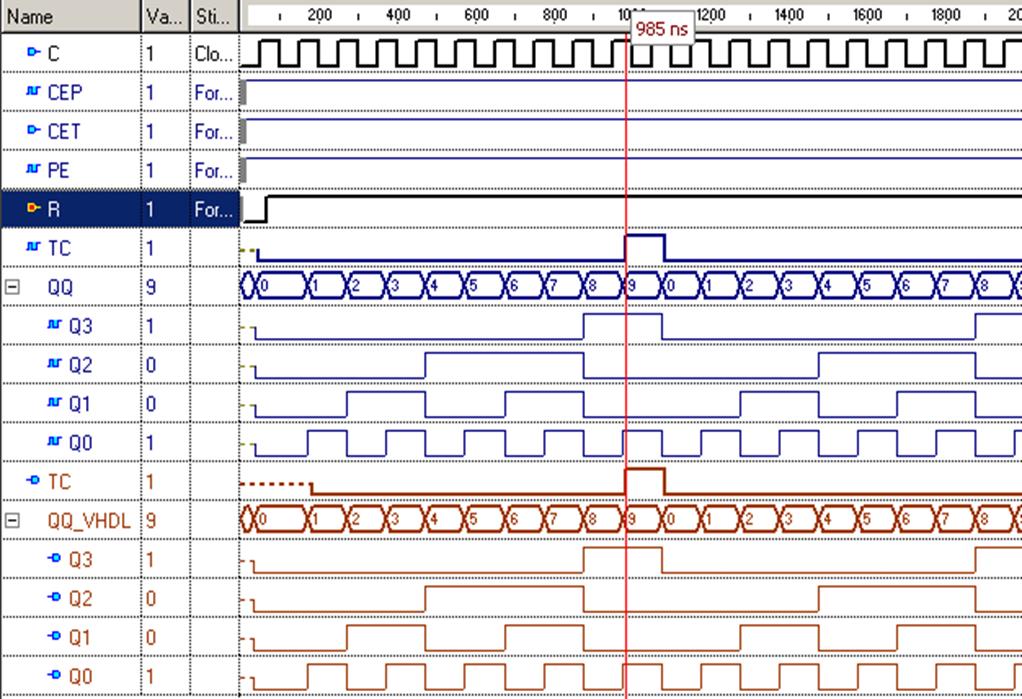

Рис. 19. Работа счетчика в режиме счета

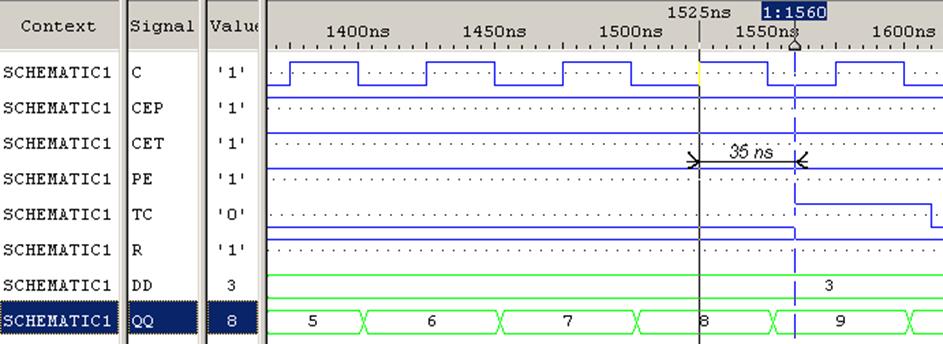

Рис. 20. Определение задержки от входа R до Q H->L

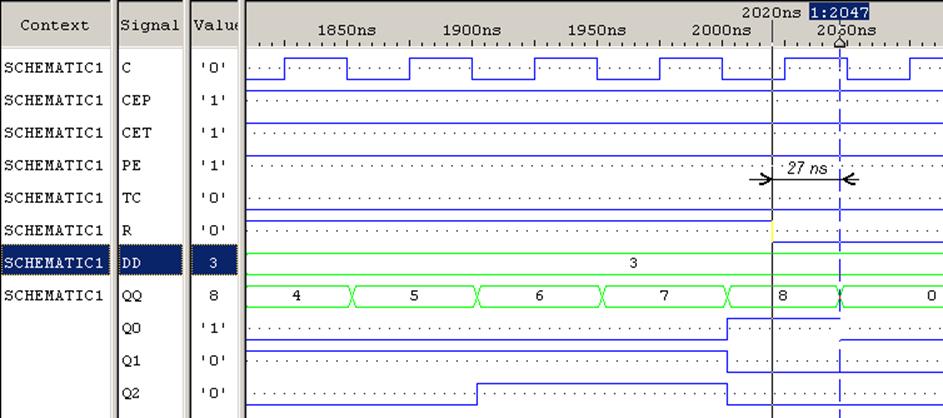

Рис. 21. Определение задержки от входа С до TC

Рис. 22. Определение задержки от входа С до Q L->H

Как видно из временных диаграмм, счетчик ИЕ9 работает правильно, с соблюдением всех задержек.

Рис. 23. УГО моделируемого узла

Рис. 24. Принципиальная схема моделируемого узла

Если говорить о поведенческой модели счетчика, то тут в Active HDL 5.1 всё делается быстро и легко. К тому же VHDL-модель писать снова нет необходимости – её можно взять из OrCad’a, что я собственно и сделал. Поэтому, чтобы не повторяться, второй раз приводить VHDL описание не буду. См. пункт 8.4.

Рис. 25. Диаграмма работы счетчика в режиме счета

Рис. 26. Задержка распространения от С до Q L->H.

Рис. 27. Задержка распространения от С до Q H->L.

Рис. 28. Задержка распространения от С до TC.

Рис. 29. Задержка распространения от R доQ

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.