.STIMULUS D STIM (4, 1111) ;! Hex

+ +0s 0100

+ 199.5ns 0001

+ 402.5ns 0000

+ 605.5ns 0010

+ 2.1315us 0110

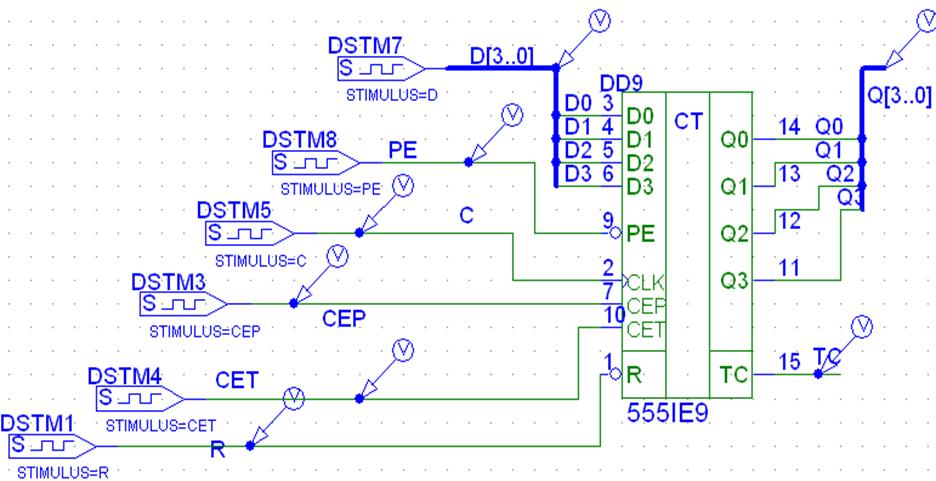

Рис. 6. Схема верификации микросхемы К555ИЕ9

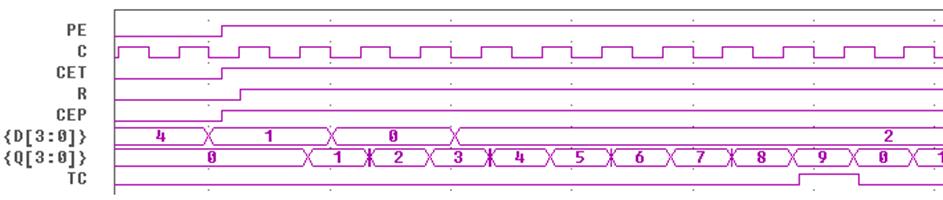

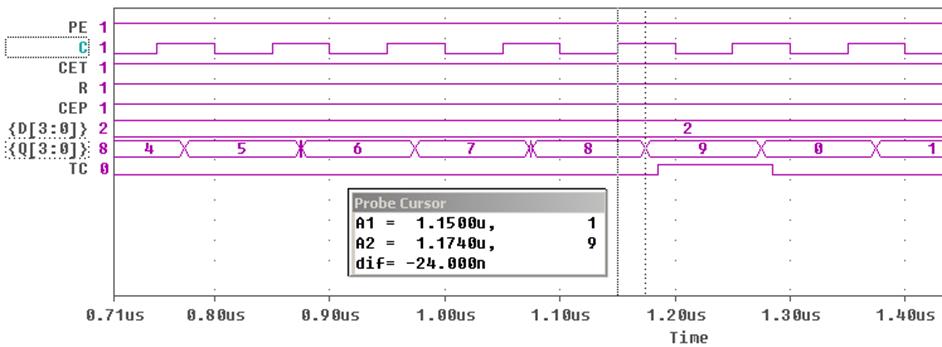

Рис. 7. Работа счетчика в режиме счета

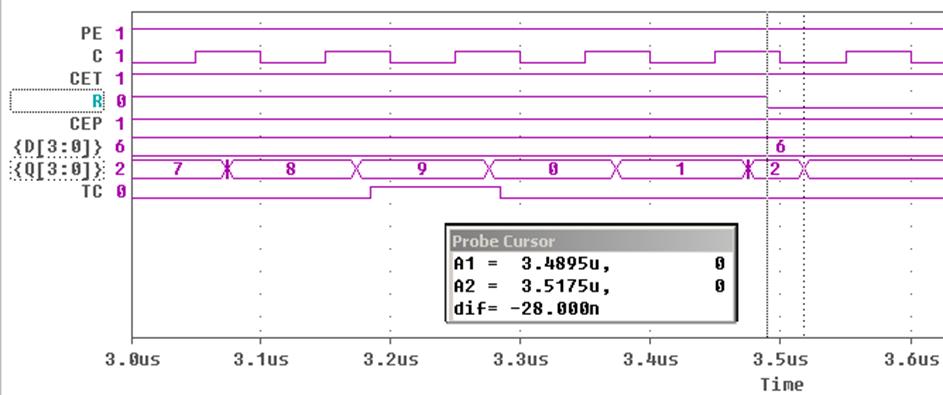

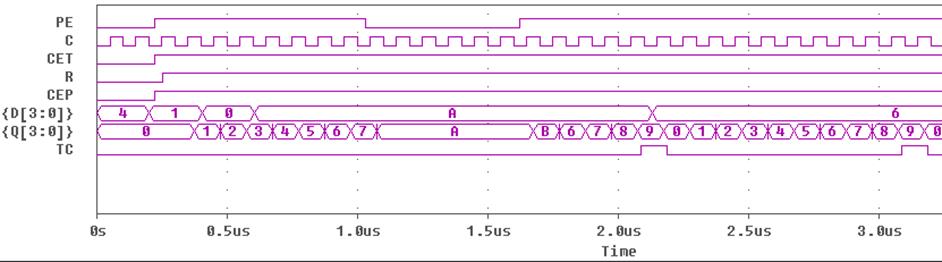

Рис. 8. Определение задержки от входа R до Q

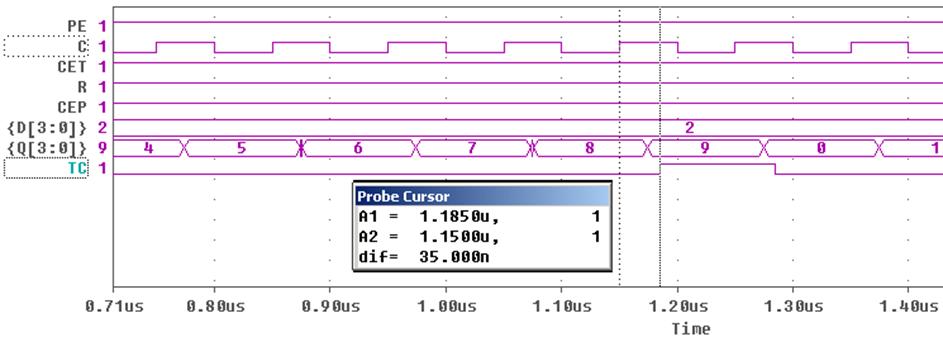

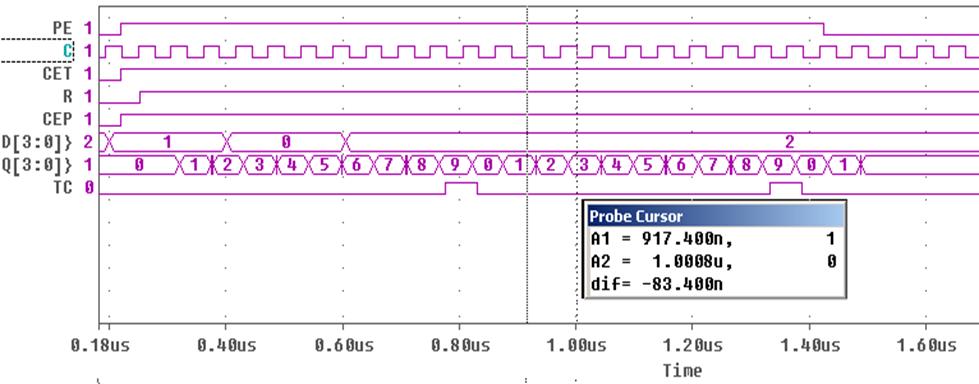

Рис. 9. Определение задержки от входа С до TC

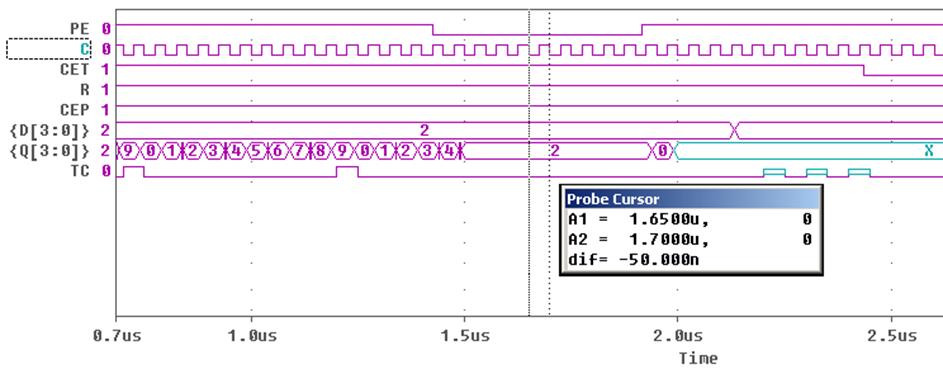

Рис. 10. Определение задержки от входа С до Q

Рис. 11. Реакция счетчика на загрузку недопустимых данных

Как видно из временных диаграмм счетчик ИЕ9 работает правильно, все временные задержки соблюдены (конечно не один в один).

Хотя предельная частота работы счетчика 555ИЕ9 составляет 25Мгц, максимальная частота моделируемого узла (при которой он стабильно работает) оказалась равной 18Мгц. Она была получена при последовательном увеличении частоты синхросигнала с 10Мгц до 18Мгц. При дальнейшем увеличении частоты синхросигнала счетчик начинает работать не стабильно.

Рис. 12. Демонстрация скоростных свойств узла. Частота сигнала C 18Мгерц.

Рис. 13. Демонстрация скоростных свойств узла. Некорректная работа узла.

* 555IE9_MAC Synchronous 4-bit Decade Counters with asynchronous clear

.SUBCKT 555IE9_MAC CLK_I CEP_I CET_I RBAR_I PEBAR_I D0_I D1_I D2_I D3_I

+ Q0_O Q1_O Q2_O Q3_O TC_O

+ OPTIONAL: DPWR=$G_DPWR DGND=$G_DGND

+ PARAMS: MNTYMXDLY=0 IO_LEVEL=0

*

ULS160ALOG LOGICEXP(13,15) DPWR DGND * БЛОКЛОГИКИ

+ CLK_I CEP_I CET_I RBAR_I PEBAR_I D0_I D1_I D2_I D3_I Q0 Q1 Q2 Q3

+ CLK CEP CET RBAR PEBAR D0 D1 D2 D3 TC DD0 DD1 DD2 DD3 CE

+ D0_GATE IO_STD IO_LEVEL={IO_LEVEL}

+ LOGIC:

+ CLK = { CLK_I } ;Buffering

+ CEP = { CEP_I }

+ CET = { CET_I }

+ RBAR = { RBAR_I }

+ PEBAR = { PEBAR_I }

+ D0 = { D0_I }

+ D1 = { D1_I }

+ D2 = { D2_I }

+ D3 = { D3_I }

+ LOAD = { ~PEBAR }

+ CE = { CEP & CET & PEBAR }

+ Q0B = { ~Q0 }

+ Q1B = { ~Q1 }

+ Q2B = { ~Q2 }

+ Q3B = { ~Q3 }

+ DD0 = { (~CE & PEBAR & Q0) | (CE & Q0B) | (LOAD & D0) }

+ DD1 = { (Q1 & ~(Q0 & CE) & PEBAR) | (Q0 & CE & Q3B & Q1B)

+ | (LOAD & D1) }

+ DD2 = { (Q2 & ~(Q1 & Q0 & CE) & PEBAR) | (Q1 & Q0 & CE & Q2B)

+ | (LOAD & D2) }

+ DD3 = { (Q3 & ~(Q0 & CE) & PEBAR) | (Q2 & Q1 & Q0 & CE & Q3B)

+ | (LOAD & D3) }

+ TC = { CET & Q0 & Q3 }

*

UDFF DFF(4) DPWR DGND $D_HI RBAR CLK DD0 DD1 DD2 DD3

+ Q0 Q1 Q2 Q3 Q0BAR Q1BAR Q2BAR Q3BAR D0_EFF IO_STD

*

ULS160ADLY PINDLY (5,0,10) DPWR DGND *БЛОКЗАДЕРЖЕК

+ TC Q0 Q1 Q2 Q3

+ CLK PEBAR CET RBAR CEP D0 D1 D2 D3 CE

+ TC_O Q0_O Q1_O Q2_O Q3_O

+ IO_STD MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

+ BOOLEAN:

+ CLOCK = { CHANGED_LH(CLK,0) }

+ CNTENT = { CHANGED(CET,0) }

+ PINDLY:

+ Q0_O Q1_O Q2_O Q3_O = {

+ CASE(

+ CLOCK & TRN_LH, DELAY(-1,24NS,24NS),

+ CLOCK & TRN_HL, DELAY(-1,27NS,27NS),

+ CHANGED_HL(RBAR,0), DELAY(-1,28NS,38NS),

+ DELAY(-1,20NS,28NS)

+ )

+ }

+ TC_O = {

+ CASE(

+ CNTENT, DELAY(-1,14NS,14NS),

+ CLOCK & TRN_LH, DELAY(-1,35NS,35NS),

+ CLOCK & TRN_HL, DELAY(-1,35NS,35NS),

+ DELAY(-1,20NS,35NS)

+ )

+ }

+ FREQ: *ЧАСТОТА И ДЛИТЕЛЬНОСТЬ СИГНАЛОВ

+ NODE = CLK

+ MAXFREQ = 25MEG

+ WIDTH:

+ NODE = CLK

+ MIN_LO = 25NS

+ MIN_HI = 25NS

+ WIDTH:

+ NODE = RBAR

+ MIN_LO = 20NS

+ SETUP_HOLD:

+ DATA(1) = PEBAR

+ CLOCK LH = CLK

+ SETUPTIME = 20NS

+ HOLDTIME = 3NS

+ WHEN = { RBAR!='0 }

+ SETUP_HOLD:

+ DATA(2) = CEP CET

+ CLOCK LH = CLK

+ SETUPTIME = 20NS

+ HOLDTIME = 3NS

+ WHEN = { RBAR!='0 & (PEBAR!='0 ^ CHANGED(PEBAR,0))

+ & CHANGED(CE,20NS) }

+ SETUP_HOLD:

+ DATA(4) = D0 D1 D2 D3

+ CLOCK LH = CLK

+ SETUPTIME = 20NS

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.