Министерство общего и профессионального образования РФ

Новосибирский государственный технический университет

Расчетно-графическая работа по дисциплине:

«Схемотехника»

«Разработка модуля памяти SRAM 8Kb, 16 bit»

Факультет: АВТ

Преподаватель: Соболев В. И. Группа: АМ-316211

Студент: Васильева

А. А.Бутузов А.В.

Новосибирск, 20054

Оглавление. 2

1. Задание: 3

2. Разработка детализированной структуры основной памяти. 3

2.1. Структурное описание основной памяти. 3

2.3.Определение

необходимого количества МС для построения модуля. 556

2.4.

Организация накопителя. 667

2.5.

Выбор интерфейсных элементов (буферов) 101011

2.5.1.

Определение коэффициентов объединения. 101011

2.5.2.

Определение нагрузки для схемы без буферов. 111112

2.5.3.

Выбор типономинала схемы согласования. 121213

2.6.

Расчёт основных параметров модуля памяти. 151516

2.7.

Временные диаграммы работы основной памяти. 161617

3. Оценка выполнения требований технического задания. 17

4. Список использованной литературы.. 18

Приложение 1. 19

Оглавление. 2

Реферат. 3

1. Задание: 4

2. Разработка

детализированной структуры основной памяти. 4

3.1. Структурное описание

основной памяти. 4

3.2. Выбор типономинала МС.. 5

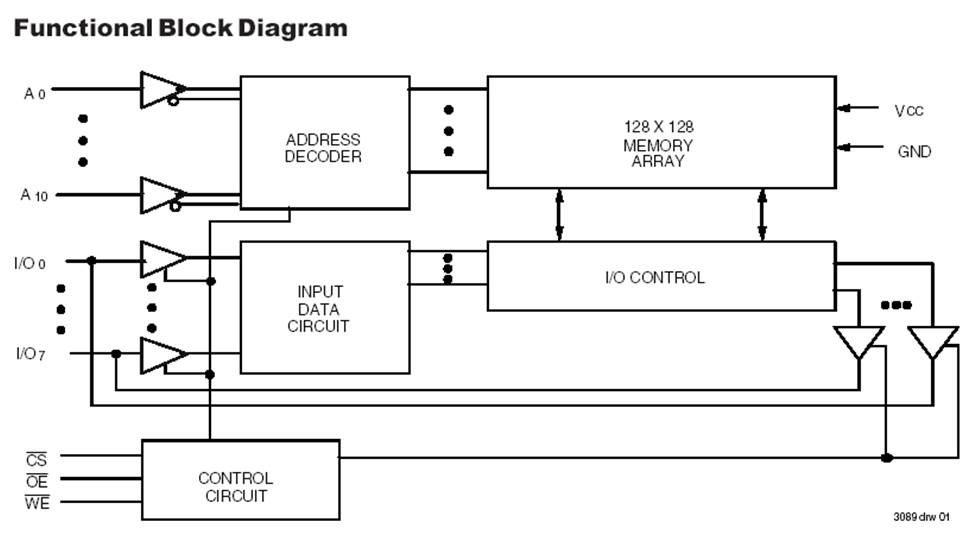

Описание выводов ИМС памяти

серии IDT6116SA (рис.2) 6

3.3.Определение

необходимого количества МС для построения модуля. 7

3.4. Организация накопителя. 8

Рисунок 2. Функциональная

схема накопителя. 9

Карта памяти. 11

3.5. Выбор

интерфейсных элементов (буферов) 12

3.6.1.

Определение коэффициентов объединения. 12

3.6.2.

Определение нагрузки для схемы без буферов. 12

3.6.3. Выбор

типономинала схемы согласования. 14

3.7. Расчёт

основных параметров модуля памяти. 15

3.8.

Временные диаграммы работы основной памяти. 15

3. Оценка выполнения

требований технического задания, 16

выводы из проделанной

работы.. 16

4. Список использованной

литературы.. 17

Приложение 2………………………………………………………………………………………...20

Данная работа

выполнена на 20-и страницах, содержит 7 рисунков и 8 таблиц, 4 приложения,

которые помогают в интерпретации решения.

Работа содержит

такие термины как линейное программирование (ЛП), целочисленное линейное

программирование (ЦЛП), целевая функция (ЦФ), метод ветвей и границ,

симплекс-метод, графический метод.

Задание

посвящено закреплению знаний полученных за семестр обучения по курсу «Методы

оптимизации». Так же в этом задании осваиваются навыки оптимизационных

вычислений при помощи различного программного обеспечения.

Спроектировать модуль памяти

типа SRAM (статическая оперативная) с информационной емкостью

8Kbk,

разрядностью слова 16 бит и временем цикла не более 120нс. Обеспечить выходной

электрический интерфейс формата ТТЛ.

Организация создаваемого модуля – (4Kx16)бит

В соответствии с требованиями расчетно-графического задания необходимо спроектировать модуль памяти, заданной информационной емкости, разрядности и быстродействия. Для подключения модуля к системе используются:

1. Шина адреса – выбирает нужное слово в адресном пространстве.

2. Шина данных – обеспечивает ввод/вывод данных по заданному адресу.

3. Управляющие сигналы для модуля памяти.

Шина

питания и «земля» не учитываются, т.к. не имеют непосредственного отношения к

структуре модуля памяти.

Выводы

шин проводятся к внешним магистралям и соединяются с ними через соответствующие

интерфейсные элементы (буферы, трансиверы).

Структурная схема!!!!!!!

32.2.

Выбор типономинала ИМСМС

Для организации указанного модуля памяти необходимо выбрать базовую микросхему памяти, которая бы максимально подходила для реализации модуля. После выбора нужно объединить эти СБИС в общую систему, выполнить обвязку шинами данных, адреса и линиями управления. Помимо этого необходимо провести выводы шин к внешним магистралям и соединить их с ними через соответствующие интерфейсные элементы (буферы, трансиверы).

Для организации создаваемого модуля – (4Kx16)бит используется модуль SRAM серии IDT6116SA. Его характеристики:

1. Информационная организация – (2Kx8)бит

2. Время доступа – 90нс.

3. Напряжение питания – 5В±10%

Память выполнена по КМОП – технологии, имеет входы и выходы совместимые с ТТЛ.

Исходя

из требований к модулю, определим количество необходимых ИМС: 4 требуются для

организации и требуемой разрядности шины слова.

Рис.унок 1. Схема

базовой ИМС памяти

серии IDT6116SA

Рис.

2 Выводы ИМС памяти

A0…А10 – входы адреса

I/O0…I/O7 –

входы/выходы данных

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.