Рис. 4. Функциональная таблица и логическое обозначение ИМС дешифратора серии SN54S139.

Данный модуль использует адреса от 0000 до FFFF. Для SRAM зарезервирована часть адресного пространства от F000 до FFFF, остальное – резерв для расширения системы памяти.

FFFF

FFFF

![]() 0FFF

0FFF

EFFF

.

.

0000

Буферы включаются в разрыв шин адреса, данных. Они служат для того, чтобы нагрузочные характеристики этих шин, подключаемых к системной магистрали соответствовали стандарту ТТЛ.

-

коэффициент объединения по входам адресов;

-

коэффициент объединения по входам адресов;

-коэффициент объединения по входам разрешения

чтения/записи;

- коэффициент объединения по входам/выходам данных;

- коэффициент объединения по входам разрешения

вывода

вывода

Определение нагрузки, создаваемой функциональными входами накопителя, функциональной шиной в отсутствии схем согласования, или буферов.

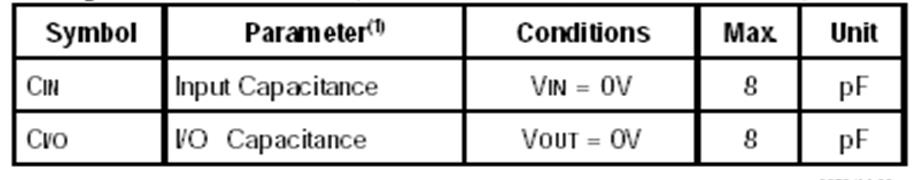

Таблица. 3. Значения емкостей входов/выходов.

Табл.ица 3. Значения емкостей входов/выходов.

|

|

|

|

||

|

||

Где

Смонт

– ….

Т.к. в данной работе используются микросхемы,

выполненные по КМОП – технологии (CMOS), то требуется учитывать

только параметры ёмкостной нагрузки,.

Т.к. в данной работе используются микросхемы,

выполненные по КМОП – технологии (CMOS), то требуется учитывать

только параметры ёмкостной нагрузки,.

Согласно стандарту ТТЛ, пиковое значение ёмкостной нагрузки не должно превышать 10 (пФ). Сравнивая это значение с полученными фактическими значениями ёмкостной нагрузки по шинам адреса, данных и управления, можем сделать вывод:

Для шин адреса, данных и сигналов управления буферизация необходима.

В качестве буфера адреса используется два 8 - разрядных однонаправленных буфера IDT74FCT244T. Первый буферизует 8 линий адреса, второй – оставшиеся 4, а также управляющие сигналы MEMR# и R/W#. Управляющие выводы буфера заземлены, буферы всегда активны.

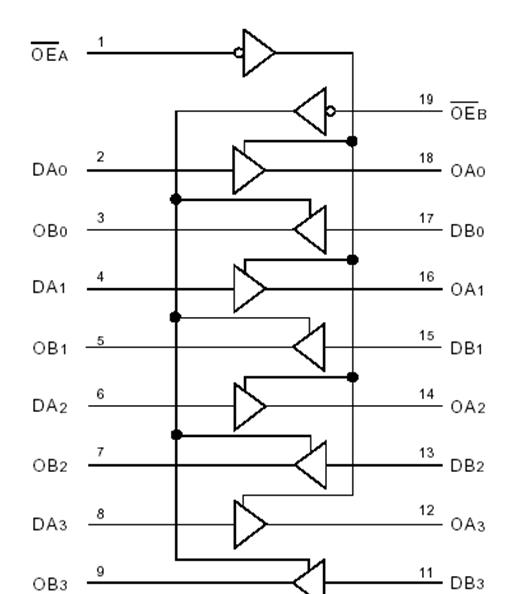

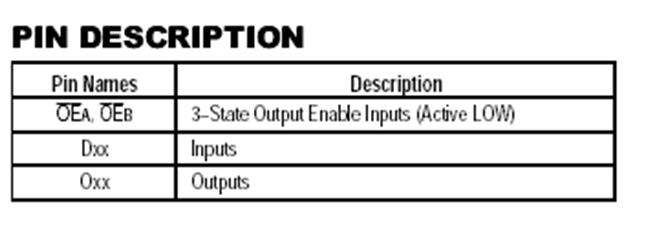

Описание функционирования буферов IDT74FCT244 (рис. 3)

Т.к сигналы разрешения вывода заземлены, буферы всегда активны. BF1 полностью использует все входы и выходы. В элементе BF2 используется лишь часть его функциональных возможностей. Неиспользуемые 2 входа второго буфера заземляются, а выходы остается свободными.

Рис. 5. Назначение

выводов, и логическое обозначение ИМС буфера серии

IDT74FCT244.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.