В качестве интерфейсного элемента на шину данных используется 16 - разрядный трансивер 74ABT16245

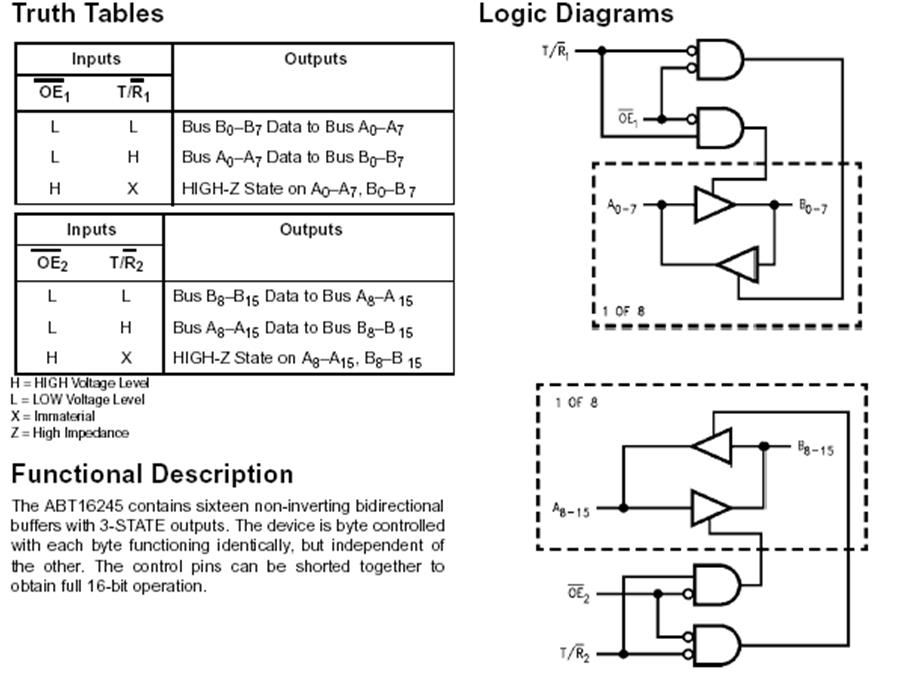

Описание функционирования трансивера 74ABT16245 (рис.3)

Трансивер составлен из двух 8 – разрядных устройств. На схеме накопителя (рис.3) на вход разрешения ввода (T/R#) подается сигнал буферизированный R/W#, на вход разрешения вывода – буферизированный MEMR#. Эти сигналы активируют трансиверы полностью (обе 8-разрядные части каждого).

Трансивер!!!!!!!!

Рис. 6. Назначение выводов, и логическое обозначение ИМС трансивера 74ABT16245.

Нормы

параметров!!!!!!!

Буферизация четырех старших битов шины адреса А12…А15

осуществляется с помощью логического вентиля.

Рис. 7. Назначение выводов, и логическое обозначение ИМС

вентиля 74HC20.

Основные параметры «4И-НЕ» 74HС20

· Напряжение питания – 5В±10%

· Время задержки сигнала – 8нс.

Схема буфера!!!!!!!!!!!!!!!

Функциональная

электрическая схема модуля памяти представлена на рис. 3 в приложении 2

Фактическая ёмкость нагрузки, создаваемая

накопителем на линии адреса, должна быть меньше допустимого значения выбранного

типономинала. Для КМОП МС, которые используются в данной работе принято, что

максимально допустимая нагрузка буфера не более 50 – ти пФ. Это устраивает нас

при принятой емкости монтажа в 10 пФ.

Выбранные типономиналы вентилей и их серии:

Фирма Texas Instruments Quad 2OR Gate (74F32) с задержкой

распространения 6 нс и инвертор (74F04) с с задержкой

распространения 7 нс.

Задержки распространения сигналов при чтении/записи в ОЗУ приведены в таблице 4

Таблица. 4. Задержки распространения в модуле.

|

Устройство |

Путь сигналов |

Задержка пути, нс. |

|

|

Чтение из ОЗУ |

Запись в ОЗУ |

||

|

IDT74FCT |

A – B |

7 |

7 |

|

|

|

|

|

|

74HC20 |

На вход G# |

8 |

8 |

|

SN54S139 |

На входы CS# |

10 |

10 |

|

|

|

|

|

|

|

Выбор адреса |

|

|

|

IDT6116SA |

Цикл записи |

|

|

|

74ABT16245 |

|

3.9 |

3.9 |

|

Максимальный путь, нс. |

Min длительность цикла, нс. |

108 |

|

Таблица Табл. 4.

Задержки распространения в модуле.

Длительность цикла основной памяти составляет 10884 нс,

что соответствует требованию к РГР.

Уровни

активности!!!!!

Более

подробные описания задержек распространения приведены в приложениях 5,6,7..

|

Параметр |

Описание |

|

A |

Адрес на внешней магистрали |

|

BF A |

Буферизированный адрес на внутренних шинах памяти |

|

OE# |

Сигнал разрешения вывода |

|

MEMR# |

Внешний сигнал активации памяти |

|

CS# |

Сигнал выбора кристалла |

|

R/W# |

Сигнал выбора чтение/запись |

|

WE# |

Прошедший буферизацию сигнал разрешения чтения/записи |

|

T/R# |

Сигнал transmit/receive трансивера |

|

DATAin |

Данные на входе SRAM |

|

DATAout |

Данные на выходе SRAM |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.