#CS –

вход выбора кристалла

#WE –

вход разрешения записи

#OE –

вход разрешения вывода

VCC –

питание

GND – «земля»

|

||

|

||

где

Nmod – ////

Nбис – ….

nmod – ////

nбис – …

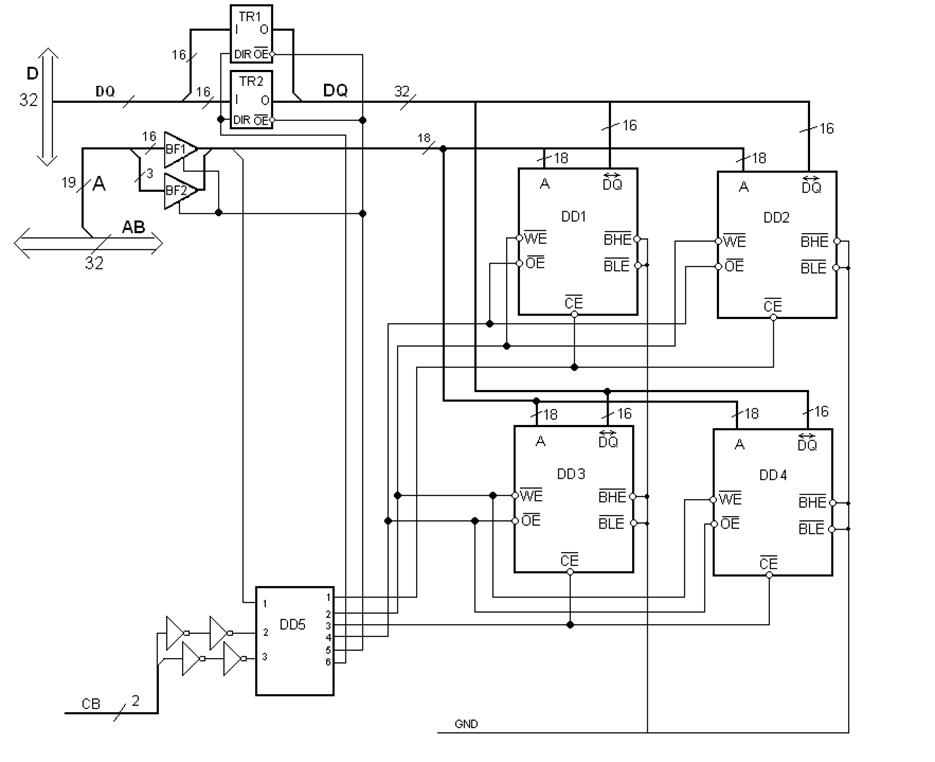

Для построения модуля памяти требуется две физических страницы – 4 ИМС IDT6116SA.

Разрядность шины адреса модуля 4Кх16 равна 12. Разрядность шины адреса ИМС памяти серии IDT6116SA – 11. Соответственно один бит А11 уйдет на декодирование для выбора физической страницы.

|

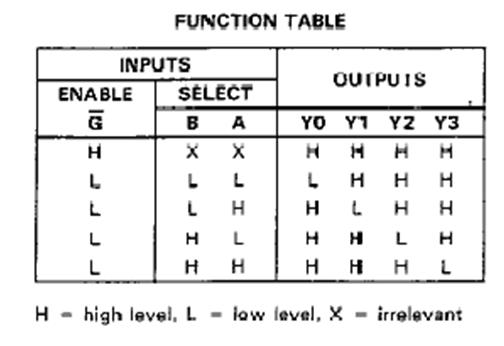

#CS |

#OE |

#WE |

DQ0…7 |

|

Состояние модуля |

|

H |

X |

X |

Состояние высокого импеданса |

|

Модуль отключен |

|

L |

L |

H |

Вывод данных |

|

Чтение слова |

|

L |

L |

L |

Ввод данных |

|

Запись по адресу |

|

L |

H |

H |

Состояние высокого импеданса |

|

Модуль выбран, выводы отключены |

|

Таблица. 2. Приложение к схеме накопителя (рис.2)

|

Обозначение |

Наименование |

Назначение |

|

DD1…4 |

Модуль SRAM памяти серии IDT6116SA |

Накопитель информации |

|

DD5 |

Логический элемент 4И-НЕ серии 74HС20 |

Декодирование 4 старших битов адреса |

|

TR |

Трансивер, серия 74ABT16245 |

Прием и передача 16 битов данных |

|

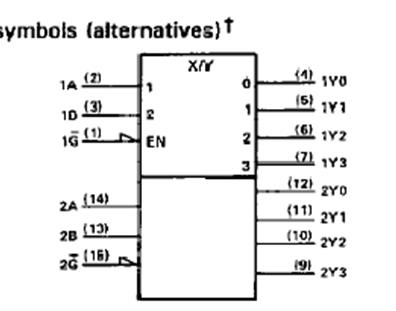

DC |

Дешифратор, серия SN54S139 |

Выбор физической страницы |

|

BF1 |

Буфер, серия IDT74FCT244 |

Передача 8 младших битов адреса |

|

BF2 |

Буфер, серия IDT74FCT244 |

Передача 4 старших битов адреса, сигналов MEMR#, R/W# |

Табл.

2.

Приложение к схеме накопителя (рис.23)

Описание выводов функциональной схемы (рис.23)

A – внутренняя шина адреса

DQ – двунаправленная внутренняя шина данных

CS# – вход выбора кристалла

WE# – вход разрешения записи

OE# – вход разрешения вывода

MEMR# - сигнал обращения к модулю памяти

АВ – системная шина адреса

DB – системная шина данных

DD1

DQ0…DQ7- младшие разряды 16-разрядного слова

A0…А10 - шина адреса

DD2

DQ8…DQ15- старшие разряды 16-разрядного слова

A0…А10 – шина адреса

DD3

DQ0…DQ7- младшие разряды 16-разрядного слова

A0…А10 - шина адреса

DD4

DQ8…DQ15- старшие разряды 16-разрядного слова

A0…А10 – шина адреса

DD5

Входы:

1 …4– старший биты шины адреса - A12…А15

Выход:

1 – сигнал управления дешифратора

Основные параметры «4И-НЕ» 74HС20

·Напряжение

питания – 5В±10%

·Время

задержки сигнала – 6нс.

Модуль памяти активен, когда сигнал MEMR# находится на низком уровне (активен), и четыре старших бита адреса равны 1. то есть модуль занимает окно памяти в верхних адресах начиная с 0FFF и до FFFF. Для дешифрации четырех старших битов используется логический элемент 4И-НЕ, серии 74HС20. Остальные сигналы управления, а именно:

MEMR# - буферизуется и поступает на входы OE# микросхем памяти.

R/W# - буферизуется и поступает на входы WE# микросхем памяти

После декодирования четырех старших бит адреса сигнал с выхода логического элемента, поступает на вход «G#» дешифратора.

C выходов дешифратора сигналы идут на входы CSOE# микросхем памяти каждой из физических страниц.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.