Новосибирский государственный технический университет

Кафедра ВТ

Пояснительная записка к курсовой работе по дисциплине «Моделирование»

Тема: «Проектирование цифрового узла в САПР DesignLab 8.0 и OrCAD 9.1»

|

|||

|

|||

Факультет: АВТ

Группа: АМ-209

Студент: Майснер М.Ю.

Преподаватель: Шалагинов А. В.

Новосибирск 2005

Содержание

1. Постановка задачи.. 3

2. Условное графическое обозначение проектируемого узла.. 3

3. Таблица назначения выводов узла.. 3

4. Логическая таблица режимов работы узла.. 4

5. Таблица реальных задержек работы узла.. 4

6. Описание работы узла.. 4

7. Моделирование узла в пакете DesignLab 8.0. 5

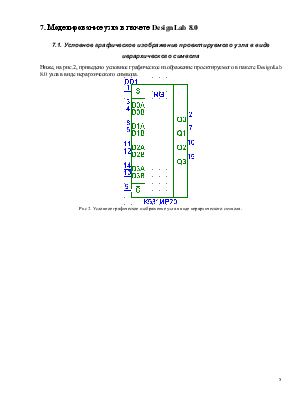

7.1. Условное графическое изображение проектируемого узла в виде иерархического символа. 5

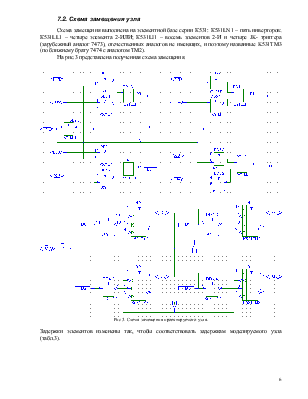

7.2. Схема замещения узла. 6

7.3. Текстовое SPICE-описание моделируемого узла. 7

7.4. Файл описания внешних воздействий. 8

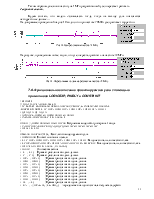

7.5. Схема верификации иерархического символа. 9

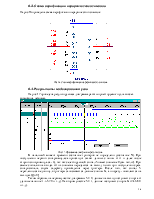

7.6. Результаты моделирования узла в пакете DesignLab 8.0. 9

7.7. Оценка предельных скоростных (частотных) возможностей. 10

исследуемого узла. 10

7.8. Функциональное описание проектируемого узла с помощью примитивов LOGICEXP, PINDLY и CONSTAINT. 11

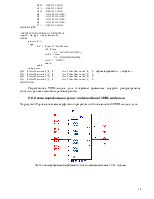

7.9. Схема верификации символа с подключённой макромоделью.. 13

7.10. Результаты моделирования символа с подключённой макромоделью.. 13

8. Моделирование узла в пакете OrCAD 9.1. 14

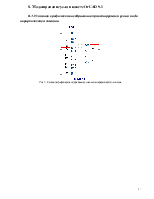

8.1. Условное графическое изображение проектируемого узла в виде иерархического символа. 14

8.2. Принципиальная схема замещения узла. 15

8.3. Схема верификации иерархического символа. 16

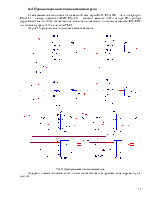

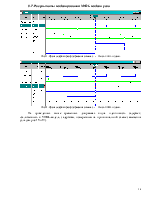

8.4. Результаты моделирования узла. 16

8.5. Поведенческая VHDL-модель узла. 17

8.6. Схема верификации узла с подключённой VHDL-моделью.. 18

8.7. Результаты моделирования VHDL-модели узла. 19

9. Выводы... 20

10. Список использованной литературы... 22

Для заданного варианта ИМС необходимо разработать цифровой узел, создать структурные и поведенческие модели в пакетах DesignLab 8.0 и OrCad 9.1. Провести имитационные эксперименты с разработанным узлом, подтвердить его работоспособность и соответствие временных задержек требуемым. Исследовать возможности используемых инструментальных средств проектирования.

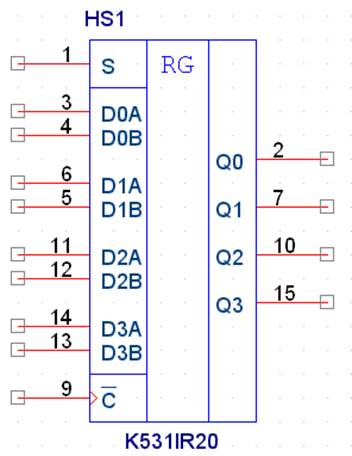

В качестве исследуемого узла вариантом задан элемент ИР20 (четырехразрядный регистр с селектором 2 в 1 на входе).

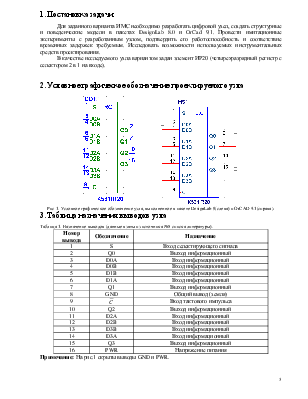

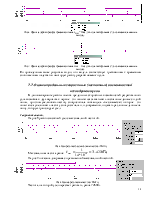

Рис 1. Условное графическое обозначение узла, выполненное в пакете DesignLab 8(слева) и OrCAD 9.1(справа).

Таблица 1. Назначение выводов (данные взяты из источника №5 списка литературы).

|

Номер вывода |

Обозначение |

Назначение |

|

1 |

S |

Вход селектирующего сигнала |

|

2 |

Q0 |

Выход информационный |

|

3 |

D0A |

Вход информационный |

|

4 |

D0B |

Вход информационный |

|

5 |

D1B |

Вход информационный |

|

6 |

D1A |

Вход информационный |

|

7 |

Q1 |

Выход информационный |

|

8 |

GND |

Общий вывод (земля) |

|

9 |

|

Вход тактового импульса |

|

10 |

Q2 |

Выход информационный |

|

11 |

D2A |

Вход информационный |

|

12 |

D2B |

Вход информационный |

|

13 |

D3B |

Вход информационный |

|

14 |

D3A |

Вход информационный |

|

15 |

Q3 |

Выход информационный |

|

16 |

PWR |

Напряжение питания |

Примечание: На рис.1 скрыты выводы GND и PWR.

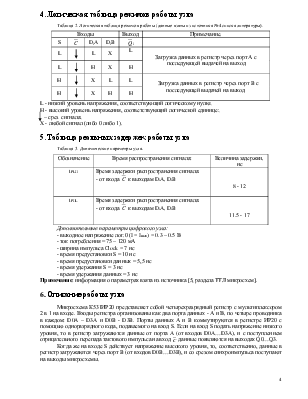

Таблица 2. Логическая таблица режимов работы (данные взяты из источника №4 списка литературы).

|

Входы |

Выход |

Примечание. |

|||

|

S |

|

DiA |

DiB |

|

|

|

L |

|

L |

X |

L |

Загрузка данных в регистр через порт А с последующей выдачей на выход |

|

L |

|

H |

X |

H |

|

|

H |

|

X |

L |

L |

Загрузка данных в регистр через порт B с последующей выдачей на выход |

|

H |

|

X |

H |

H |

|

L - низкий уровень напряжения, соответствующий логическому нулю;

![]() H - высокий уровень напряжения, соответствующий логической

единице;

H - высокий уровень напряжения, соответствующий логической

единице;

– срез сигнала;

X - любой сигнал (либо 0 либо 1).

Таблица 3. Динамические параметры узла.

|

Обозначение |

Время распространения сигнала: |

Величина задержки, нс |

|

tPLH |

Время задержки распространения сигнала: - от входа |

8 - 12 |

|

tPHL |

Время задержки распространения сигнала: - от входа |

11.5 - 17 |

Дополнительные параметры цифрового узла:

- выходное напряжение лог.0 (I = Imax) = 0.3 – 0.5 В

- ток потребления = 75 – 120 мА

- ширина импульса Clock = 7 нс

- время предустановки S = 10 нс

- время предустановки данных = 5,5 нс

- время удержания S = 3 нс

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.