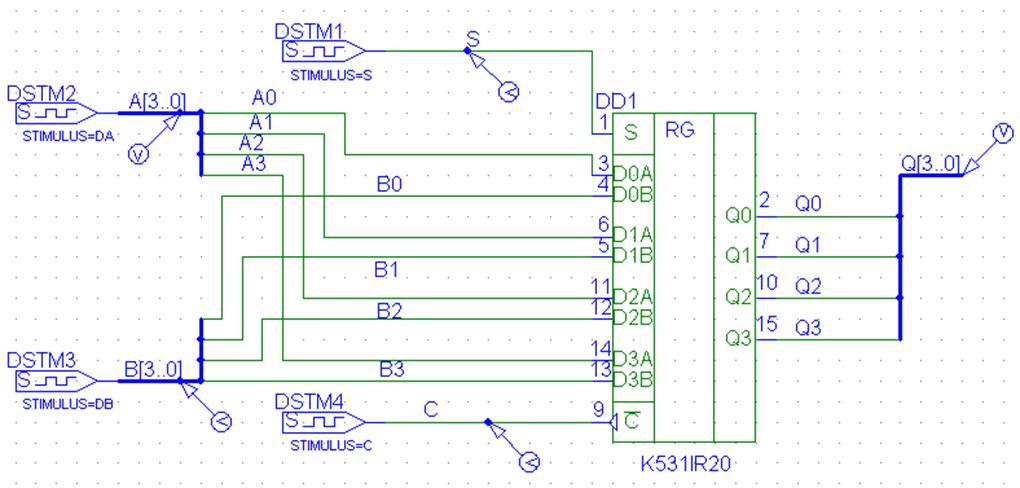

На рис.4 приведена схема верификации иерархического символа:

Рис 4. Схема верификации иерархического символа

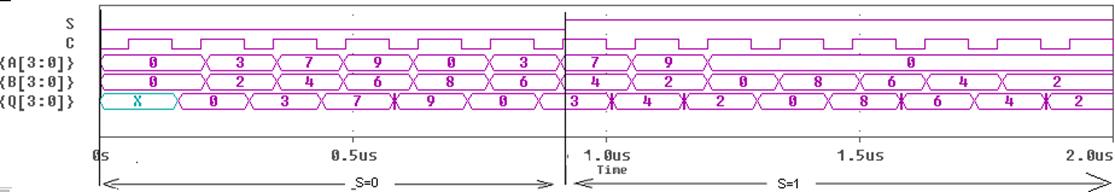

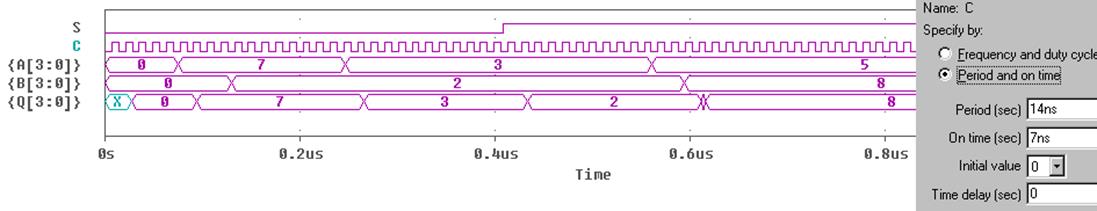

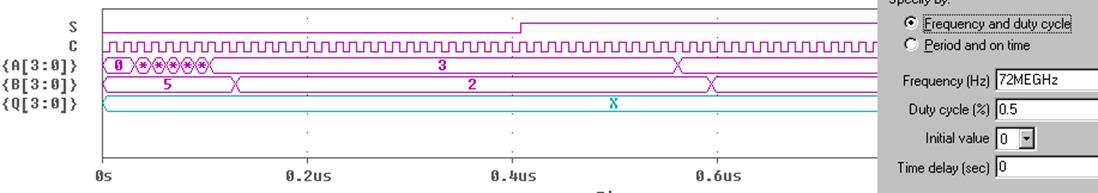

На рис.5 приведена результирующая диаграмма работы проектируемого узла во всех возможных режимах.

Рис 5. Временные диаграммы моделирования узла

В начальный момент времени состояние триггеров не определено (состояние X). При поступлении первого синхроимпульса происходит захват данных с шины A (0 и далее после второго синхроимпульса - 3), так как селектирующий сигнал S имеет значение 0 (см. табл.2). При смене сигналов на входах Ai их значения передаются на выход только при поступлении среза синхросигнала, спустя задержку прохождения через триггеры. После того, как сигнал S переключился в единицу, в триггеры записываются данные с шины Bi, а по срезу - появляются на выходах Q[3:0].

Таким образом, на первом участке диаграммы S = 0, данные на выход поступают с порта A (данные на шине: 0,3,7,9,0). На втором участке S = 1, данные поступают с порта B (4,2,0,8,6…).

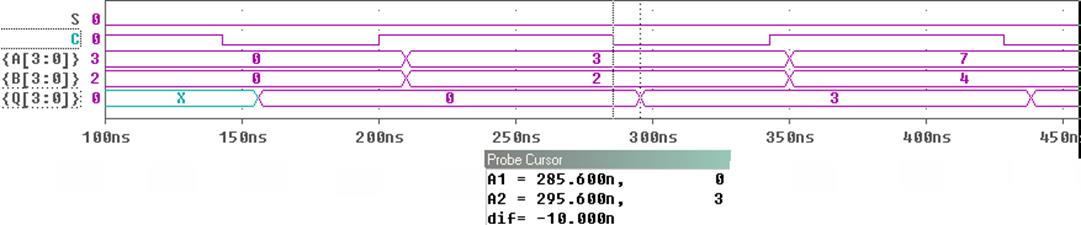

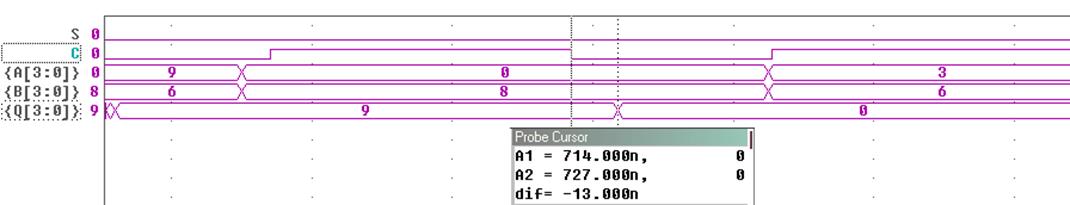

Ниже, на рис.6 и рис.7 показаны величины задержек распространения сигнала от входа С к выходам Q:

Рис 6. Время задержки распространения сигнала tPLH = 10нс (от входа тактирования С до появления данных на выходе).

Рис 7. Время задержки распространения сигнала tPHL = 13нс (от входа тактирования С до появления данных на выходе).

По приведенным выше рисункам видно, что модель соответствует требованиям к временным соотношениям и адекватно имитирует работу разрабатываемого узла.

В данном варианте работы оценка предельных скоростных возможностей разработанного узла возможна в двух вариантах: первое – это попытаться захватывать постоянные данные с одной шины, при этом увеличивать частоту синхросигнала пока модель «не сломается»; и второе – это попытаться увеличивать частоту синхросигнала и, одновременно, подавать различные данные на шину, которую транслирует узел.

1 вариант оценки.

На рис.8 работоспособный узел с максимальной частотой.

Рис 8.Узел работает без ошибок на частоте 71 МГц.

Максимальная

частота равна:

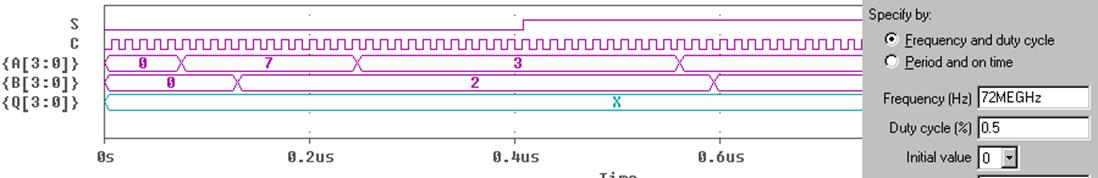

На рис.9 показана диаграмма с превышенной максимальной частотой.

Рис 9.Узел не работает на частоте 72 МГц.

Частота, на которой узел перестает работать, равна 72МГц.

Таким образом, увеличив частоту на 1МГц разработанный узел перестает работать.

2 вариант оценки.

Будем считать, что модель «сломалась» тогда, когда на выходе узла появляются некорректные данные…

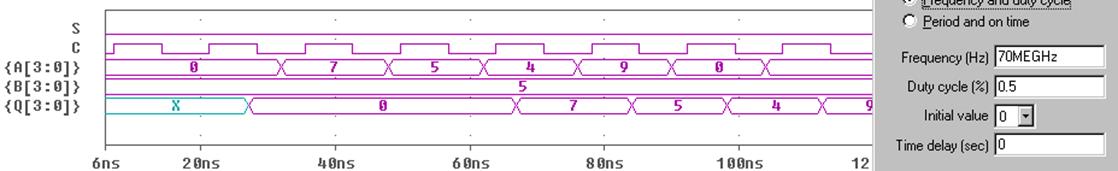

На диаграмме, приведенной на рис.10 видно, что при частоте 70МГц узел работает корректно.

Рис 10.Узел работает на частоте 70 МГц.

На рисунке, приведенном ниже, видно, что узел перестал работать на частоте 72МГц.

Рис 10. Разработанная модель не работает на частоте 72 МГц.

* K531IR20

** THE TTL DATA BOOK, 1988, TI

* TC 08/25/92 REMODELED USING LOGICEXP, PINDLY, & CONSTRAINT DEVICES

.SUBCKT K531IR20 S_I C_I D0A_I D0B_I D1A_I D1B_I D2A_I D2B_I D3A_I D3B_I

+ Q0_O Q1_O Q2_O Q3_O

+ OPTIONAL: DPWR=$G_DPWR DGND=$G_DGND

+ PARAMS: MNTYMXDLY=0 IO_LEVEL=0

*

U1 JKFF(4) DPWR DGND $D_HI $D_HI CLK ;Встроенная модель JK-триггера на 4 входа

+ JA JB JC JD KA KB KC KD QA QB QC QD $D_NC $D_NC $D_NC $D_NC

+ D0_EFF IO_STD

*

U298LOG LOGICEXP(10,18) ;Блок логики моделируемого узла

+ DPWR DGND ;Контакты питания и земли

+ S_I C_I D0A_I D0B_I D1A_I D1B_I D2A_I D2B_I D3A_I D3B_I ;Входные сигналы логического блока

+ S C D0A D0B D1A D1B D2A D2B D3A D3B JA JB JC JD KA KB KC KD ; Выходные сигналы логического блока + D0_GATE IO_STD IO_LEVEL={IO_LEVEL}

+ LOGIC: ;Логическая секция

+ S = { S_I } ;Прямая трансляция входных данных

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.