D3B : IN STD_LOGIC;

Q0 : OUT STD_LOGIC;

Q1 : OUT STD_LOGIC;

Q2 : OUT STD_LOGIC;

Q3 : OUT STD_LOGIC;

\C\\\ : IN STD_LOGIC);

END K531IR20;

ARCHITECTURE MODEL OF K531IR20 IS

signal Y : std_logic_vector(3 downto 0);

BEGIN

process (\C\\\)

begin

if \C\\\='0' and \C\\\'EVENT then

if S='0' then

Y <= (D3A,D2A,D1A,D0A);

elsif S='1' then

Y <= (D3B,D2B,D1B,D0B);

else Y <= "UUUU";

end if;

end if;

end process;

Q0 <= '0' after 12ns when Y(0) = '0' else '1' after 12ns when Y(0) = '1'; - первая задержка это tPLH, вторая tPHL.

Q1 <= '0' after 12ns when Y(1) = '0' else '1' after 12ns when Y(1) = '1';

Q2 <= '0' after 12ns when Y(2) = '0' else '1' after 12ns when Y(2) = '1';

Q3 <= '0' after 12ns when Y(3) = '0' else '1' after 12ns when Y(3) = '1';

END MODEL;

Разработанная VHDL-модель узла отображает временные задержки распространения сигналов для всех возможных режимов работы.

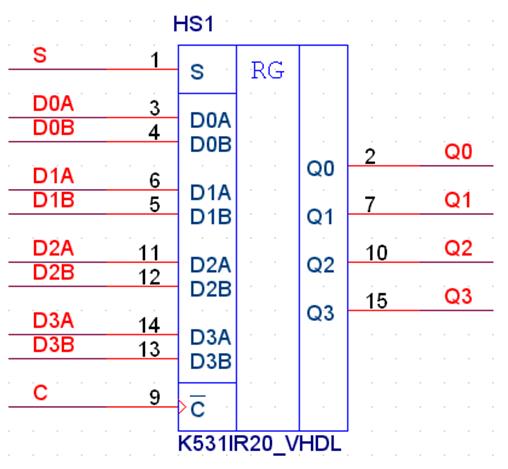

На рисунке 20 приведена схема верификации разработанной поведенческой VHDL-модели узла.

Рис 20. Схема верификации разработанного узла с подключенной к нему VHDL-моделью.

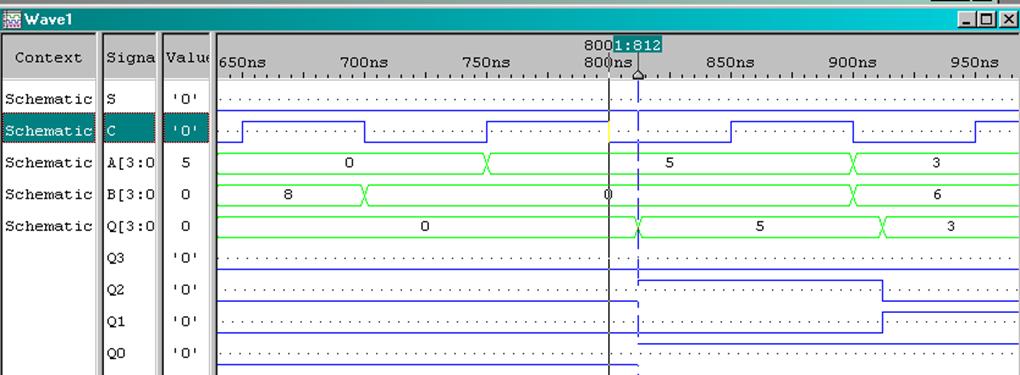

Рис 21. Время задержки распространения сигнала tPLH = 12нс в VHDL-модели.

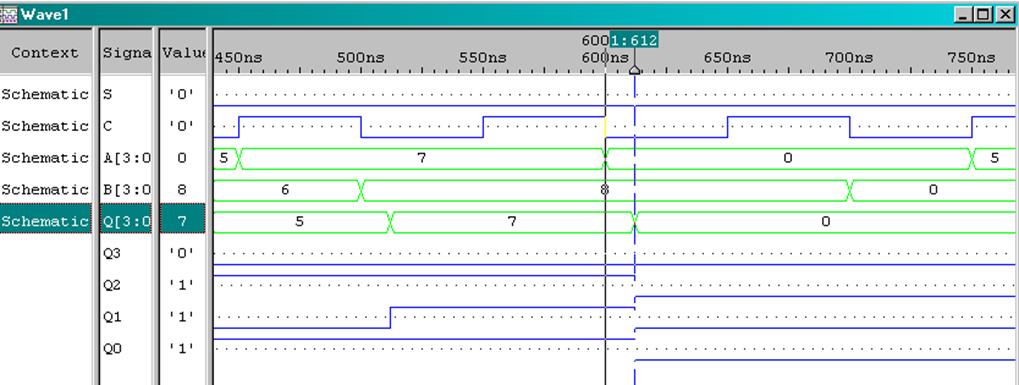

Рис 22. Время задержки распространения сигнала tPHL = 12нс в VHDL-модели.

На приведенных выше временных диаграммах видна идентичность задержек, «заложенных» в VHDL-модель, задержкам, измеренным на принципиальной схеме замещения узла (см. рис.18 и 19).

В ходе выполнения данной курсовой работы было выполнено индивидуальное задание по разработке цифрового узла ИР20 (четырехразрядный регистр с мультиплексором 2 в 1 на входе), созданию его структурных и поведенческих моделей (на языках SPICE, DSL, VHDL в пакетах DesignLab 8 и OrCAD 9.1). Были проведены имитационные эксперименты с разработанным узлом, целью которых являлось подтверждение работоспособности узла и соответствие его временных задержек требуемым. Не пройденный на лабораторных работах в прошлом семестре пакет ActiveHDL 6.1 мне не представилась возможность изучить из-за нехватки временного ресурса.

Проведение имитационных экспериментов, про которые говорилось выше, сопутствовалось использованием одинаковых диаграмм входных сигналов. Данный метод обеспечивает наглядность идентичности всех задержек, вне зависимости от того строился ли элемент на основе схемы замещения или в виде макромодели(VHDL-модели).

Курсовая работа выполнялась в течении трех недель. При выполнении использовалось руководство к курсовой работе[1], выданное в прошлом семестре. Работа в пакете DesignLab 8.0 осуществлялась около двух недель, а третья неделя была посвящена работе в пакете OrCAD 9.1.

По проделанной работе был закреплен имеющийся опыт проектирования в перечисленных САПР, получены дополнительные навыки и знания по разработке цифровых узлов.

Говоря о пакетах САПР можно выделить следующее:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.