.ENDS ;Конец макромодели

*

*$

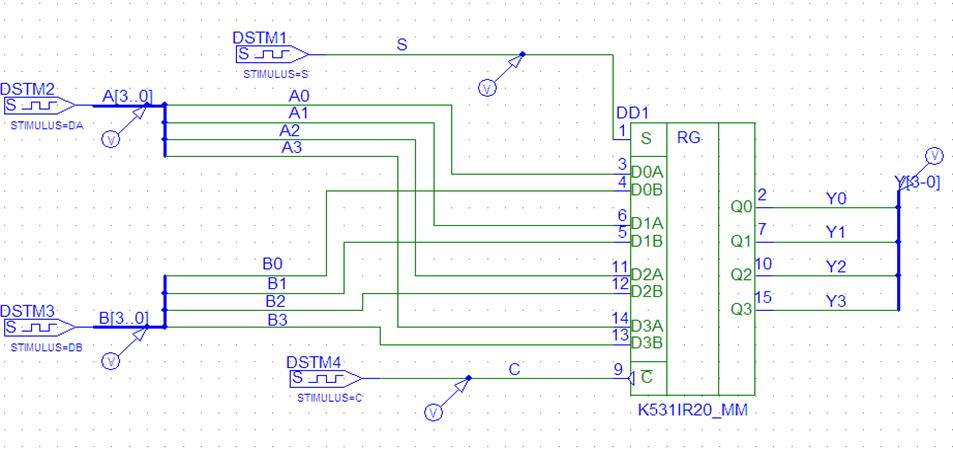

На рис.11 приведена схема верификации разработанной модели K531IR20_MM. Ее функциональное описание приведено в пункте 7.8.

Рис 11. Схема верификации символа с подключённой макромоделью

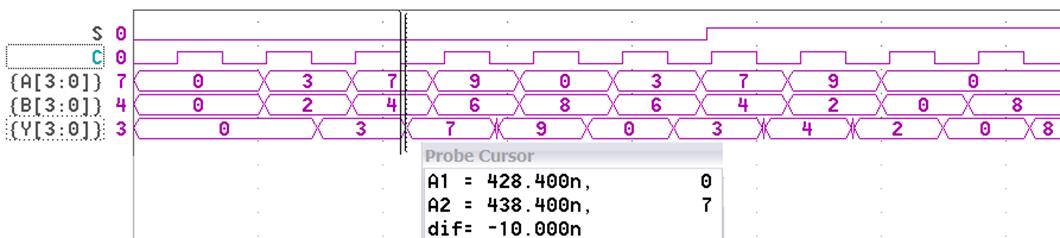

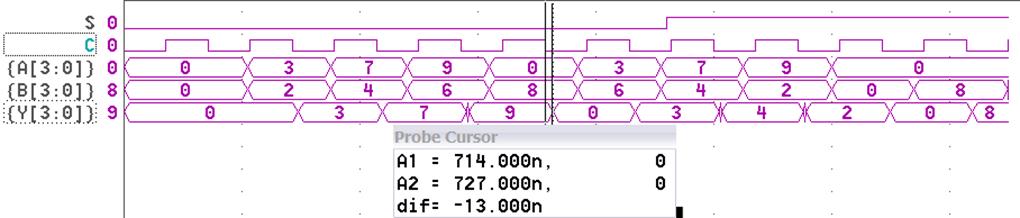

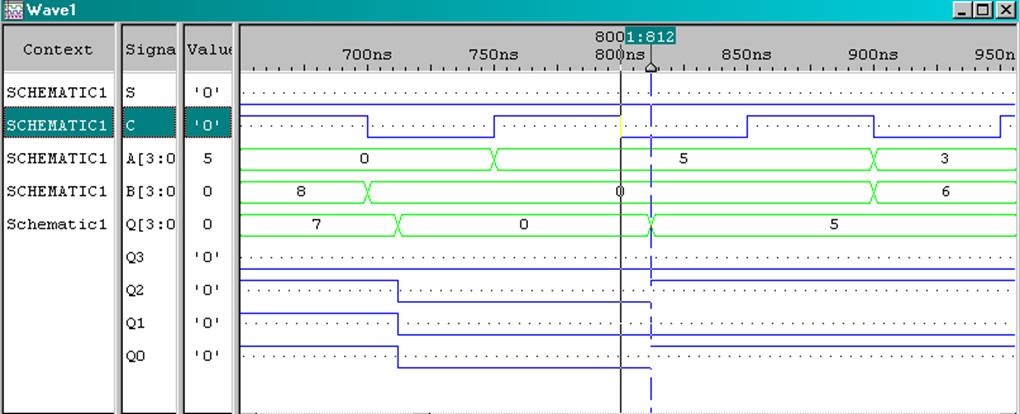

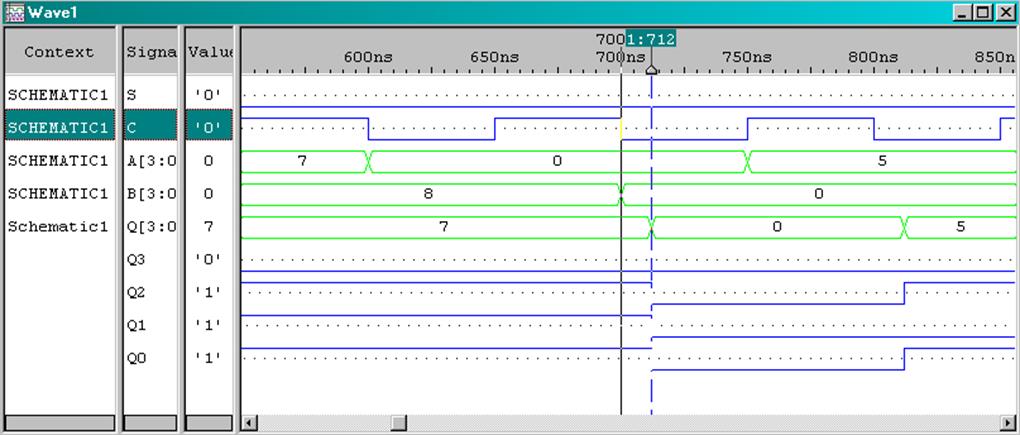

На рис.12 и 13 приведены временные диаграммы работы разработанного узла с подключенной макромоделью. Задержки соответствуют требуемым и совпадают с задержками на рис.6 и 7.

Рис 12. Временная диаграмма работы узла с подключённой макромоделью. Задержка tPLH = 10нс.

Рис 13. Временная диаграмма работы узла с подключённой макромоделью. Задержка tPHL = 13нс.

По приведенным диаграммам видно, что разработанный узел работает корректно и воспроизводит все режимы работы реальной ИМС с соответствующими временными задержками.

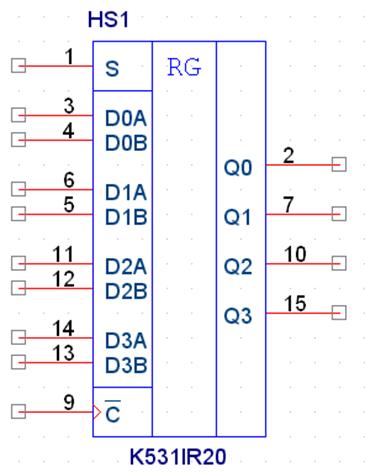

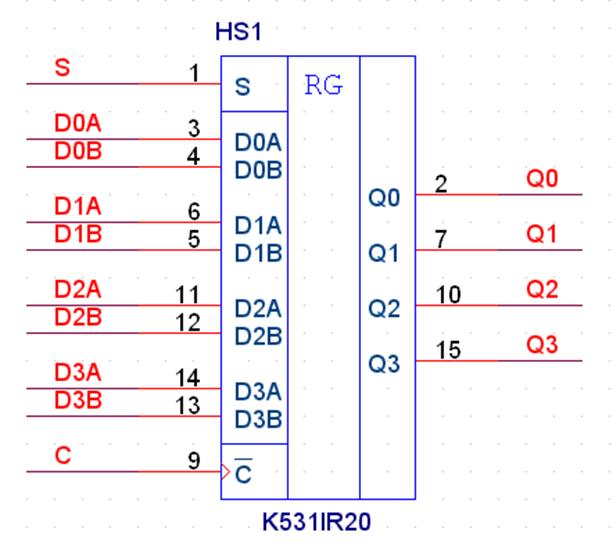

Рис 14. Условное графическое изображение узла в виде иерархического символа

Схема замещения выполнена на элементной базе серии К531: К531LN1 – пять инверторов; К531LL1 – четыре элемента 2-ИЛИ; К531LI1 – восемь элементов 2-И и четыре JK- триггера (зарубежный аналог 7473), отечественных аналогов не имеющих, и поэтому названные K531TM3 (по ближнему брату 7474 с аналогом TM2).

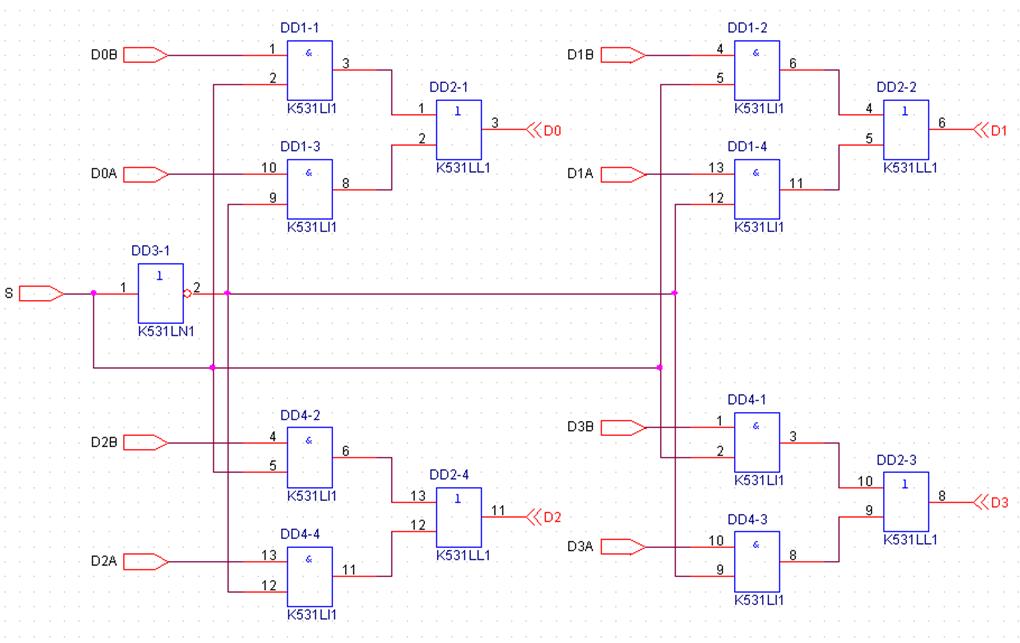

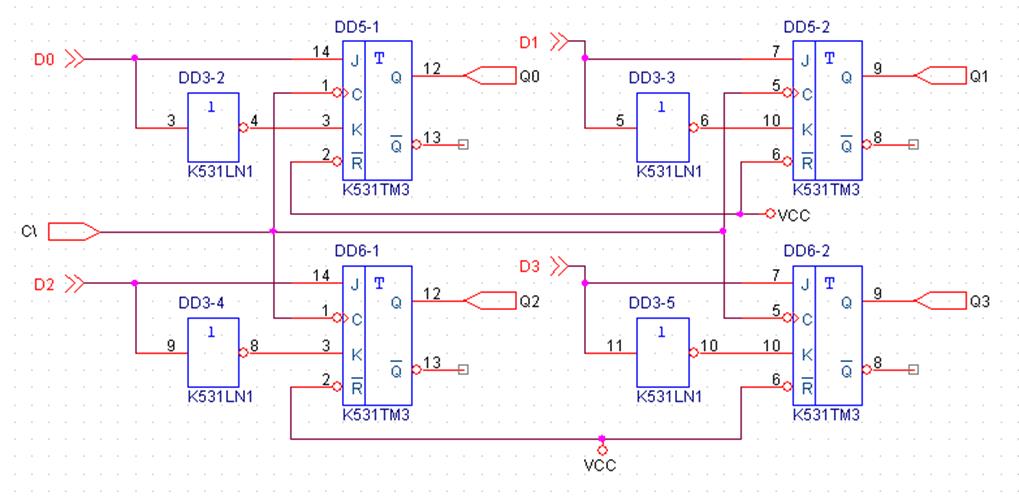

На рис.15 представлена полученная схема замещения.

Рис 15. Принципиальная схема замещения узла

Задержки элементов изменены так, чтобы соответствовать задержкам моделируемого узла (табл.3).

На рис.16 приведена схема верификации иерархического символа:

Рис 16. Схема верификации иерархического символа

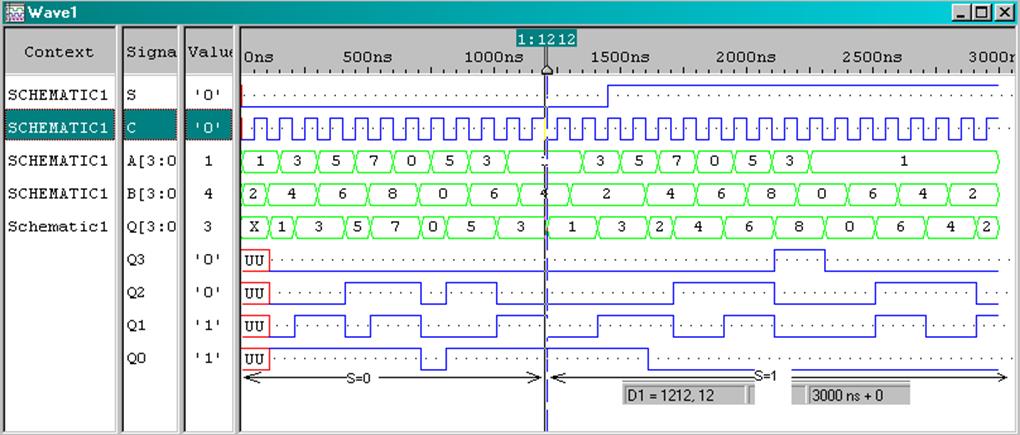

На рис.17 приведена результирующая диаграмма работы проектируемого узла во всех возможных режимах.

Рис 17. Временные диаграммы работы узла.

В начальный момент времени состояние триггеров не определено (состояние X). При поступлении первого синхроимпульса происходит захват данных с шины A (1 и далее после второго синхроимпульса - 3), так как селектирующий сигнал S имеет значение 0 (см. табл.2). При смене сигналов на входах Ai их значения передаются на выход только при поступлении среза синхросигнала, спустя задержку прохождения через триггеры. После того, как сигнал S переключился в единицу, в триггеры записываются данные с шины Bi, а по срезу - появляются на выходах Q[3:0].

Таким образом, на первом участке диаграммы S = 0, данные на выход поступают с порта A (данные на шине: 1,3,5,7,0 и т.д.). На втором участке S = 1, данные поступают с порта B (2,4,6,8,0 и т.д.).

Ниже, на рис.18 и рис.19 показаны величины задержек распространения сигнала от входа С к выходам Q:

Рис 18. . Время задержки распространения сигнала tPLH = 12нс (от входа тактирования С до появления данных на выходе).

Рис 19. Время задержки распространения сигнала tPHL = 12нс (от входа тактирования С до появления данных на выходе).нс).

По приведенным диаграммам видно, что разработанный узел работает корректно и воспроизводит все режимы работы реальной ИМС с соответствующими временными задержками.

Library ieee;

Use ieee.std_logic_1164.all;

Use ieee.numeric_std.all;

ENTITY K531IR20 is

PORT (

S : IN STD_LOGIC;

D0A : IN STD_LOGIC;

D0B : IN STD_LOGIC;

D1A : IN STD_LOGIC;

D1B : IN STD_LOGIC;

D2A : IN STD_LOGIC;

D2B : IN STD_LOGIC;

D3A : IN STD_LOGIC;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.