Введемо слідуючу систему

кодування: 00 – всі канали справні; 11; 1,0; 01 – відмовив відповідно перший

канал “a”;

другий канал “b”;

третій канал ”c”.

Введемо слідуючу систему

кодування: 00 – всі канали справні; 11; 1,0; 01 – відмовив відповідно перший

канал “a”;

другий канал “b”;

третій канал ”c”.

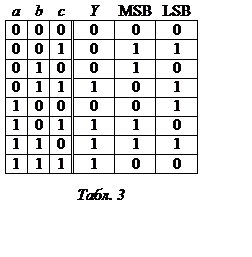

Тепер можна побудувати таблицю станів вузла.(Таб. 3)

З таблиці відомими засобами знаходимо:

![]()

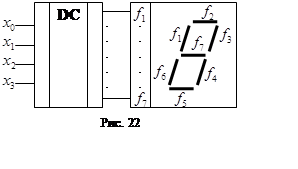

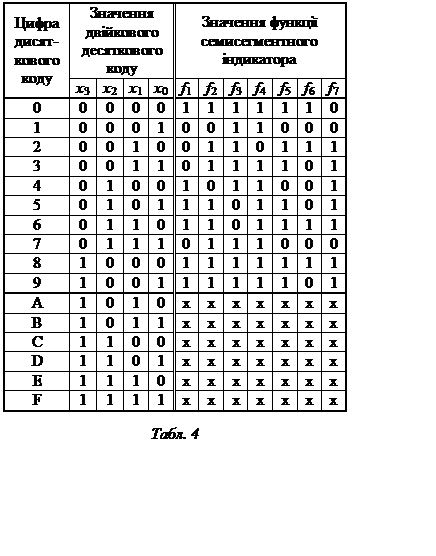

60. На рис. 22 приведена схема включення перетворювача коду. Підсвітка кожного із елементів індикатора, утворюючих десяткові числа від 0 до 9 відбувається шляхом подачі одиничного сигналу на відповідний його вхід.

Для

побудови логічної схеми індикатора необхідно створити таблицю істиності

логічних функцій перетворювача (див. табл. 4).

Для

побудови логічної схеми індикатора необхідно створити таблицю істиності

логічних функцій перетворювача (див. табл. 4).

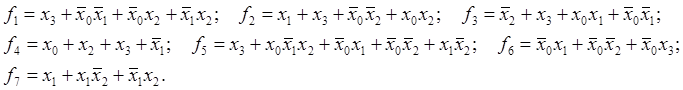

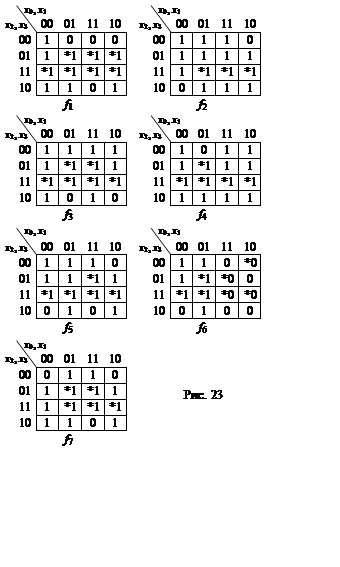

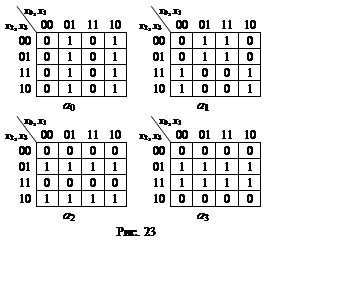

Специфіка таблиці 4 в тому, що частина значень двійково десяткового коду не визначена Це дозволяє спростити значення функцій f1-f7 Для мінімізації функцій f1-f7 представимо іх за допомогою карт Карно. (рис. 23).

Для мінімізації логічних функцій f1-f7 незаповнені клітини необхідно довизначити. Через те, що значення функцій відповідаючих цим клітинам для нас немають значення, ми можимо записати в ни як одиниці, так і нулі, виходячи лише із умови отримання мінімальної форми логічних функцій.

Довизначивши значення функцій в відповідності з рис. 23 після мінімізації маємо:

Реалізація цих функцій в вибраному базисі елементів відбувається за допомогою засобів, описаних в попередній задачі.

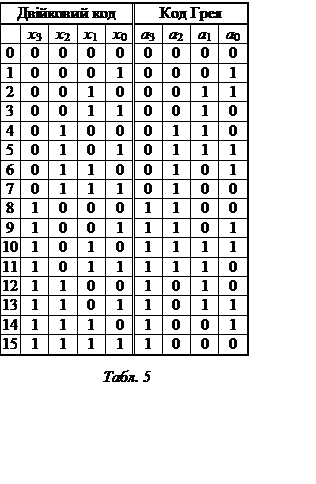

61. Код Грея називається одношаговим і його характерною особливістю є те, що при переході до наступної кодової комбінації змінюється тільки одна цифра. Його застосування дозволяє забезпечити високу точність перетворення різного роду механічних переміщень в цифровий код.

Таблиця відповідності двійкового чотирьохрозрядного і коду Грея (табл. 5) дозволяє встановити логічний звязок між ними.

Відповідна карта Карно приведена на рис. 24.

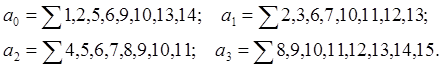

Після мінімізації маємо:

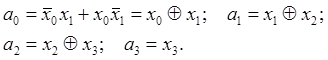

Таким чином перетворення двійкового коду в код Грея відбувається елементом ВИКЛЮЧАЮЧЕ АБО (рис. 25а).

|

Задача перетворення коду Грея в двійковий

вирішується аналогічно. Результуюча схема перетворювача відповідає рисунку

25б.

Задача перетворення коду Грея в двійковий

вирішується аналогічно. Результуюча схема перетворювача відповідає рисунку

25б.

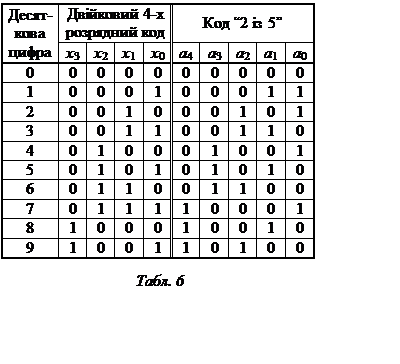

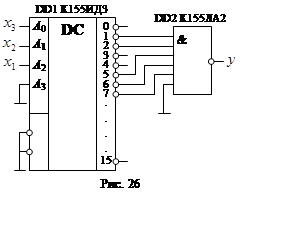

62.  Код

“2 з 5” використовується для безпомилкової передачі цифрової інформації. В

цьому п’ятирозрядному коді кожна допустима комбінація містить дві одиниці, й

оскільки таких комбінацій десять, то кожна з них відповідає одній десятковій

цифрі. Так як точно дві одиниці повинні бути в цьому коді, код “2 з 5” має

захист від помилок, які виникають при передачі його в цифровому каналі зв’язку.

(див. табл. 6)

Код

“2 з 5” використовується для безпомилкової передачі цифрової інформації. В

цьому п’ятирозрядному коді кожна допустима комбінація містить дві одиниці, й

оскільки таких комбінацій десять, то кожна з них відповідає одній десятковій

цифрі. Так як точно дві одиниці повинні бути в цьому коді, код “2 з 5” має

захист від помилок, які виникають при передачі його в цифровому каналі зв’язку.

(див. табл. 6)

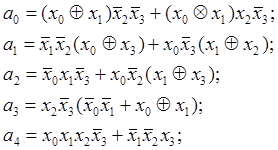

Мінімізуючи функції а0…а4 отримаємо вирази для вихідних сигналів:

які легко реалізувати використовуючи елементи ВИКЛЮЧАЮЧЕ АБО.

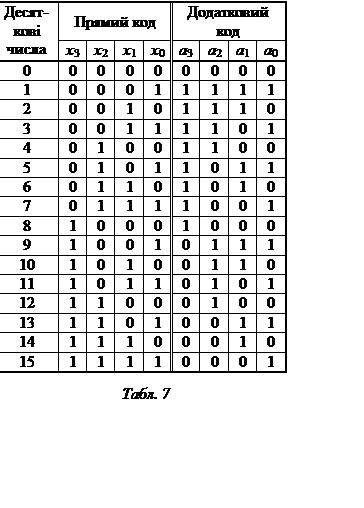

63.  Додаткові

коди утворюються із прямого Х шляхом інвертування прямого коду й

додавання до нього 1 молодшого розряду

Додаткові

коди утворюються із прямого Х шляхом інвертування прямого коду й

додавання до нього 1 молодшого розряду ![]() . В

результаті маємо таблицю відповідності кодів (табл. 7).

. В

результаті маємо таблицю відповідності кодів (табл. 7).

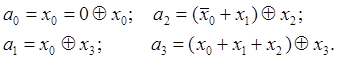

Мінімізуючи логічні функції а0-а3 за допомогою карт Карно находимо мінімізовані вирази вихідних функції.

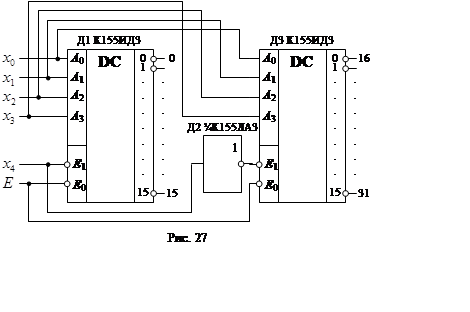

64. Для реалізації функції приведемо іі до досконалої дизюнктивної нормальної форми:

![]()

Використовуючи шестивходовий елемент К155ЛА2 І-НЕ отримуємо схему, яка буде реалізовувати захисну функцію (рис. 26).

65.

|

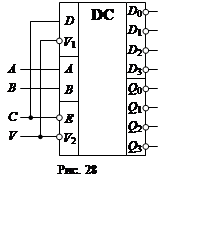

66.  Якщо входи A, B, C використовувати

як адресні (рис. 28), а інформацію подавати на вход V,

данна мікросхема буде працювати як дешифратор який складається із трьох входів А,

В, С на вісім виходів.

Якщо входи A, B, C використовувати

як адресні (рис. 28), а інформацію подавати на вход V,

данна мікросхема буде працювати як дешифратор який складається із трьох входів А,

В, С на вісім виходів.

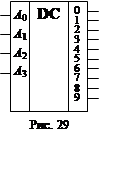

67.  Дешифратор 564ИД1 виконує перетворення 4-х розрядного

двійкового коду в вихідний сигнал високого рівня на одному з 10 виходів. Із

таблиці істиності мікросхеми маємо, що при зміні двійкового коду в інтервалі

значень, відповідаючих десятковим числам 0-9 має місце однозначна

відповідність вхідного двійкового коду й сигналу високого рівня на відповідному

виході 0-9. При значеннях вхідного двійкового коду більших 1001 виходи 0-7

мають нульовий вихідний сигнал. Таким чином мікросхема дозволяє однозначно

виконувати дешифрацію трьохрозрядного двійкового коду на один з 8 виходів при

наявності нуля на вході А3 (рис. 29). При наявності сигналу

високого рівня на вході А3 виходи 0-7 будуть відключені.

Тобто вхід А3 може виконувати функцію входу, який дозволяє роботу

мікросхеми з декодування інформації, яка надходить на входи А0,

А1, А2.

Дешифратор 564ИД1 виконує перетворення 4-х розрядного

двійкового коду в вихідний сигнал високого рівня на одному з 10 виходів. Із

таблиці істиності мікросхеми маємо, що при зміні двійкового коду в інтервалі

значень, відповідаючих десятковим числам 0-9 має місце однозначна

відповідність вхідного двійкового коду й сигналу високого рівня на відповідному

виході 0-9. При значеннях вхідного двійкового коду більших 1001 виходи 0-7

мають нульовий вихідний сигнал. Таким чином мікросхема дозволяє однозначно

виконувати дешифрацію трьохрозрядного двійкового коду на один з 8 виходів при

наявності нуля на вході А3 (рис. 29). При наявності сигналу

високого рівня на вході А3 виходи 0-7 будуть відключені.

Тобто вхід А3 може виконувати функцію входу, який дозволяє роботу

мікросхеми з декодування інформації, яка надходить на входи А0,

А1, А2.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.