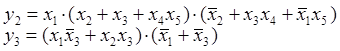

43. Мінімізувати функції та реалізувати їх у базисі І-НЕ:

44. ![]()

![]() Використовуючи елементи І-НЕ, реалізувати наступні

функції, не використовуючи прийоми мінімізації:

Використовуючи елементи І-НЕ, реалізувати наступні

функції, не використовуючи прийоми мінімізації:

45. ![]() Реалізувати

наступну функцію на елементах І-НЕ, що мають не більше трьох входів:

Реалізувати

наступну функцію на елементах І-НЕ, що мають не більше трьох входів:

46. ![]() Використовуючи

елементи АБО-НЕ, реалізувати наступні булеві функції:

Використовуючи

елементи АБО-НЕ, реалізувати наступні булеві функції:

|

47. ![]() Реалізувати

на елементах АБО-НЕ, що мають не більше трьох входів наступну функцію:

Реалізувати

на елементах АБО-НЕ, що мають не більше трьох входів наступну функцію:

48. Реалізувати логічну схему з непарною кількістю входів т, яка дозволяє вирішити задачу голосування простою більшістю. Розв’язати задачу для т=3, 5.

49. При розробці електронного календаря виникає необхідність кодування днів тижня. Пропонується довільно закодувати дні тижня та розробити логічну схему їх інкодування.

50.

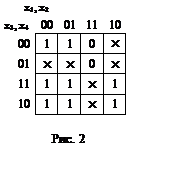

![]() Для

логічної функції, що задана картою Карно (рис. 2), значення функції у клітинках

зі значком ´ є недовизначеними. Довизначити функцію з

метою отримання мінімальної диз’юнктивної форми.

Для

логічної функції, що задана картою Карно (рис. 2), значення функції у клітинках

зі значком ´ є недовизначеними. Довизначити функцію з

метою отримання мінімальної диз’юнктивної форми.

51. Для недовизначеної функції, що задана картою Карно (рис. 2), скласти логічну функцію семантичного контролю.

52. Визначити величину часової затримки трьох послідовно включених мікросхем К155ЛА3 та порівняти з результатами затримок аналогічних мікросхем серій К555, 1533, К561.

53. ![]() На

логічних мікросхемах серії К155 побудувати декілька вріантів схем, що

реалізують

логічну функцію . Оцінити розроблені схеми по

велечині затримки Т та по

апаратурним витратам W.

На

логічних мікросхемах серії К155 побудувати декілька вріантів схем, що

реалізують

логічну функцію . Оцінити розроблені схеми по

велечині затримки Т та по

апаратурним витратам W.

54.  Використовуючи мікросхеми з відкритим колектором,

розробити схеми, “монтажне АБО”, “монтажне І”.

Використовуючи мікросхеми з відкритим колектором,

розробити схеми, “монтажне АБО”, “монтажне І”.

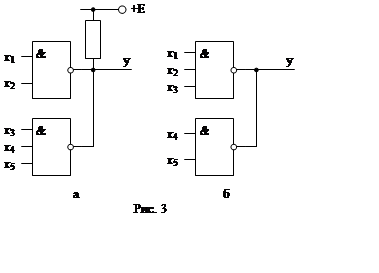

55. На рис. 3 приведені логічні схеми монтажної логіки. Пояснити, які логічні операції вони реалізують.

56. Забезпечити розголудження сигналу на число елементів, що перевищує коефіцієнт розгалудження по виходу елементу, що служить джерелом сигналу. Дати розв’язки як для невеликої кратності перевищення, так і для перевищення в десяткі разів.

57. На елементах серії К155 побудувати схему, яка реалізує операцію 16 І; операцію 16 АБО.

58. Побудувати схему додавання по модулю 2 на вісім входів, використовуючи двовходові суматори по модулю 2.

59. Побудувати схему вузла мажорування 2 з 3, що відновлює інформацію при відмові одного з трьох каналів. Побудувати вузел, що дозволяє виявити канал, що відмовив.

60. Розробити логічну схему перетворювача двійково-десяткового коду у семирозрядний код керування семисегментними цифровими індикаторами.

61. Розробити програму перетворювача двійкового чотирьохрозрядного коду в код Грея та код Грея у двійковий.

62. Розробити перетворювач двійкового чотирьохрозрядного коду в код 2 з 5 та коду 2 з 5 у код двійковий.

63. Розробити перетворювач прямого чотирьохрозрядного двійкового коду в код додатковий.

64. ![]()

![]() Використовуючи дешифратор К155ИД3, призначеного для

перетворення чотирьохрозрядного двійкового коду в напругу низького логічного

рівня, що з’являється на одному з шістнадцяти виходів реалізувати

логічну функцію

Для реалізації функції використовувати багатовходові логічні елементи з множини

І-НЕ, АБО-НЕ, І, АБО.

Використовуючи дешифратор К155ИД3, призначеного для

перетворення чотирьохрозрядного двійкового коду в напругу низького логічного

рівня, що з’являється на одному з шістнадцяти виходів реалізувати

логічну функцію

Для реалізації функції використовувати багатовходові логічні елементи з множини

І-НЕ, АБО-НЕ, І, АБО.

65. Використовуючи дешифратор К155ИД3 та додаткові логічні входи, розробити принципову схему аналогічного дешифратора, призначеного для перетворення п’ятирозрядного коду х1–х5 в напрузі низького рівня на одному з 32 входів.

66. Використовуючи мікросхему К155ИД4 розробити: а) принципову схему демультиплексора 1:8; б) дешифратора 3:8.

67. Використовуючи дешифратори серії 564ИД1 розробити принципову схему дешифрації шестирозрядного двійкового коду на 64 вихода.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.