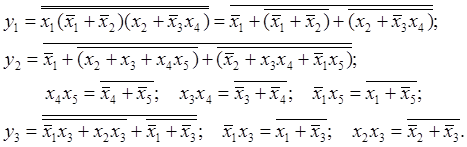

46. Перетворемо вхідні функції:

На рис. 16 приведена схема, яка реалізує функцію у1 у базисі АБО-НЕ.

47. Функція, шляхом застосування подвійного заперечення може бути перетворена до виду:

![]()

|

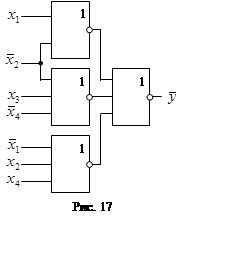

Варіант реалізації фунцкії приведено на

рис. 17.

Варіант реалізації фунцкії приведено на

рис. 17.

48. Вказівка. Щодо застосування тривхідного логічного елемента, ця задача зводиться до того, що на виході його повинна з’явитися 1 у трьох випадках, коли у наборі х1х2х3 не менш ніж дві одиниці.

52. Вказівка. Величина часової затримки визначається сумою середніх часів затримки t розповсюдження сигналу t = ½(tфр + tс) та наводиться у довідковій літературі.

53. Апаратурні витрати часто оцінюють відношенням площин корпусів чи чисел їх інформаційних виводів.

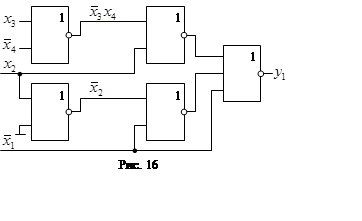

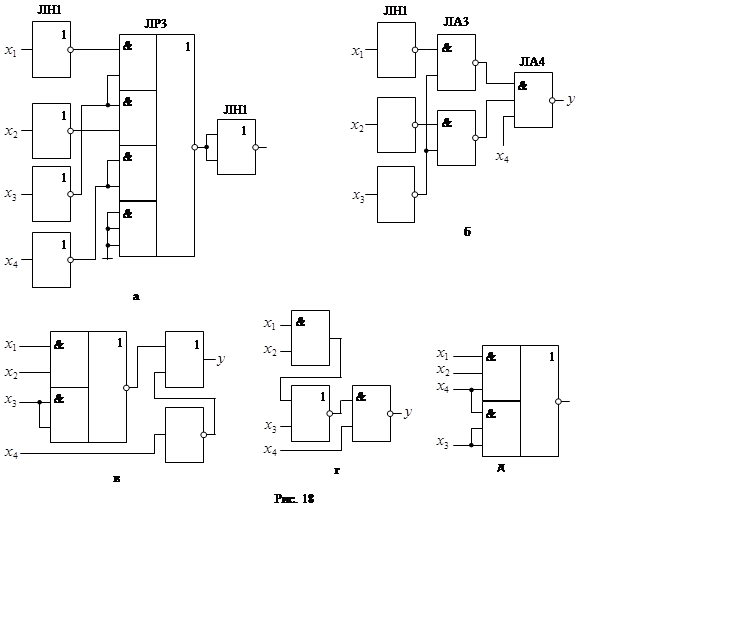

На рис. 18а приведена пряма схемна

реалізація логічної функції з використанням елементів ЛН1 та ЛН3. Так як

відповідно до довідкової літератури затримки розповсюдження сигналу елементів

ЛН1 та ЛН3 однакові, то затримки всієї схеми Т 3t. Апаратурні затрати складаються з п’яти інверторів

ЛН1, кожний з яких займає 1/6 корпуса елемента

І-АБО-НЕ-ЛР3, який займає цілий корпус. Тому  корпуса.

корпуса.

(Оцінка затрат у 1/12 корпуса чисельно близька до оцінки по сумі інформаційних входів та виходів мікросхеми.)

Невикористані елементи частково зайнятого корпуса не враховуються, так як можуть бути використані у інших схемах.

|

Формула може бути використана у трохи іншому вигляді:

![]() .

.

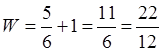

Схема, яка реалізує таку форму запису функції приведена на рис. 18в, для якої Т = 2t; W = 11/12 корпуса.

Ще одна форма представлення дає: ![]() . Відповідна схема приведена на рис. 18г,

для якої Т = 3t; W = 9/12.

. Відповідна схема приведена на рис. 18г,

для якої Т = 3t; W = 9/12.

Можна отримати ще один варіант формули: ![]() . Схема, яка реалізує цю формулу приведена

на рис. 18д та має Т = 1t; W = 12/12.

. Схема, яка реалізує цю формулу приведена

на рис. 18д та має Т = 1t; W = 12/12.

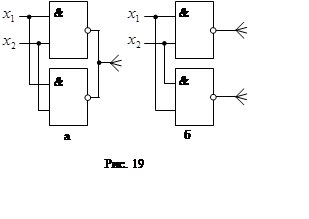

56.  На рис. 19

показані можливі варіанти схем. Просте запаралелювання елементів (рис. 19а) в

ТТЛ серіях допускається як виключення не більш, ніж для двох елементів, при

цьому вважається, що результюючий коефіцієнт розголудження збільшується лише в

1,9 раза. Обидва елемента повинні бути розміщені в одному корпусі, в іншому

випадку виникаючі вирівнюючі струми можуть викликати збої в інших ланцюгах. В

МДП-серіях обмежень на кількість запаралелюваних елементів не вводиться.

На рис. 19

показані можливі варіанти схем. Просте запаралелювання елементів (рис. 19а) в

ТТЛ серіях допускається як виключення не більш, ніж для двох елементів, при

цьому вважається, що результюючий коефіцієнт розголудження збільшується лише в

1,9 раза. Обидва елемента повинні бути розміщені в одному корпусі, в іншому

випадку виникаючі вирівнюючі струми можуть викликати збої в інших ланцюгах. В

МДП-серіях обмежень на кількість запаралелюваних елементів не вводиться.

В схемі рис. 19б кількість буферних елементів обмежується можливим навантаженням джерел сигналів. Коефіцієнт розголудження може досягнути сотні.

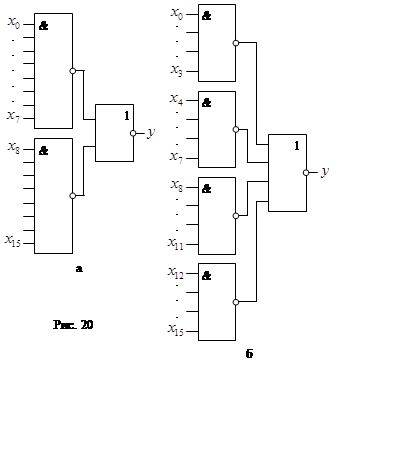

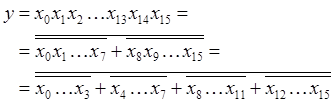

57.  Найкраще вирішення

дає розклад функції за допомогою формули де-Моргана на такі групи, розмір яких

відповідає числу входів існуючих елементів:

Найкраще вирішення

дає розклад функції за допомогою формули де-Моргана на такі групи, розмір яких

відповідає числу входів існуючих елементів:

З перетвореної формули слідують такі варіанти реалізаціі (рис. 20а,б). Матеріал даного прикладу ілюструє наступне правило: по можливості вибирати розклади, що використовують більше багатовхідних елементів.

58. Вказівка.

Врахувати той факт, що операція ВИКЛЮЧАЮЧЕ АБО підпорядковується об’єднуючому

закону ![]() що дозволяє реалізацію функції, яка

розглядається, здійснити як лінійним нарощуванням входів, так і шляхом побудови

пірамідальної структури.

що дозволяє реалізацію функції, яка

розглядається, здійснити як лінійним нарощуванням входів, так і шляхом побудови

пірамідальної структури.

59. Пояснення. Важливою задачею при передачі цифрової інформації є задача забезпечення її достовірності. Одним з прийомів підвищення достовірності даних є утроєння каналів передачі.

Вихідні сигнали

всіх трьох сигналів поступають на спеціальний вузол (мажоритарний вузол), який

формує з них вихідний сигнал за принципом голосування “2 з 3” та на двох

виходах у вигляді кодової комбінації вказує на пошкоджений канал.

Вихідні сигнали

всіх трьох сигналів поступають на спеціальний вузол (мажоритарний вузол), який

формує з них вихідний сигнал за принципом голосування “2 з 3” та на двох

виходах у вигляді кодової комбінації вказує на пошкоджений канал.

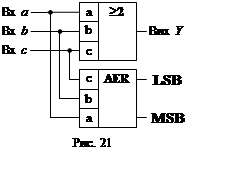

Розв’язок. З урахуванням викладенного в поясненні можна побудувати функціональну схему мажоритарного вузла (рис. 21), де зображено: AER addres erray – адреса помилки; LSB – least significant bit; BSB – most significant bit – відповідно молодший та старший розряди індикації коду відказавшого каналу.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.