|

Y1 |

Y2 |

Микрооперация |

|

0 |

0 |

Передача |

|

0 |

1 |

V |

|

1 |

1 |

|

Рисунок 5.10 – Кодировка микроопераций

Составляем таблицу истинности для дальнейшего синтеза (рис. 5.11)

|

Xвх |

Y1 |

Y2 |

Q(t) |

Q(t+1) |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

|

0 |

1 |

0 |

0 |

* |

- |

|

0 |

1 |

0 |

1 |

* |

- |

|

0 |

1 |

1 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

0 |

* |

- |

|

1 |

1 |

0 |

1 |

* |

- |

|

1 |

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

0 |

Рисунок 5.11 – Таблица истинности для синтеза регистра

На основании словаря переходов Т-триггера (рис. 5.12) заполняем колонку с сигналом T* - выходным сигналом комбинационной схемы

|

Q(t) |

T |

Q(t+1) |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

1 |

0 |

|

1 |

0 |

1 |

Рисунок 5.12 – Словарь переходов Т - триггера

Составим и минимизируем функцию для сигнала Т*. Путем склеивания

получаем минимальную форму

![]() ,

,

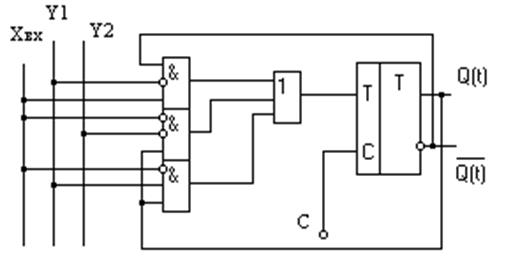

по которой составляем комбинационную схему одного разряда регистра (рис. 5.13)

Рисунок 5.13 – Схема одного разряда регистра

По такому алгоритму регистры хранения можно создавать для выполнения различных микроопераций на триггерах любого типа.

Регистры сдвига.

Служат для сдвига кода слова, занесённого в регистр. В зависимости от направления сдвига регистры делят на:

1) регистры со сдвигом вправо.

2) регистры со сдвигом влево.

3) реверсивные регистры.

Причём, различают ещё и сдвиги - арифметические, логические и циклические.

При арифметическом сдвиге смещаются все разряды кода, кроме знакового (крайнего левого бита). При логическом сдвиге смещаются все разряды кода, включая знаковый бит. При циклическом сдвиге крайние разряды соединены между собой, поэтому выдвигающийся бит помещается на освободившееся место.

При арифметическом и логическом сдвигах выдвигающиеся биты теряются, а освободившиеся места заполняются нулями.

Микрооперация сдвига записывается следующим образом:

Y1: P2:= сдв ЛП (2) P2 - сдвиг логический вправо на два бита содержимого регистра Р2

Y2: P1:= сдв АЛ (1) P1 - сдвиг арифметический влево на один бит содержимого регистра Р1

Y3: RG: = сдв ЦП (1) RG – сдвиг циклический вправо на один бит содержимого регистра RG.

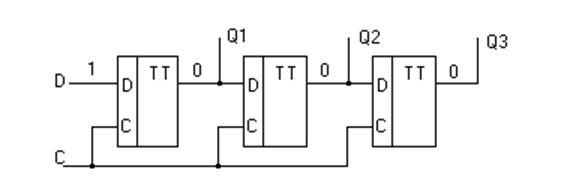

Регистр сдвига наиболее просто выполнить на D – триггерах (рис. 5.14).

Рисунок 5.14 – Регистр сдвига

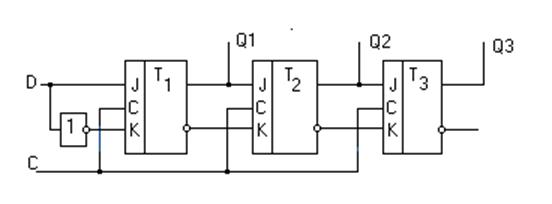

С приходом синхроимпульса код смещается вправо на один разряд. Регистр сдвига можно выполнить на JK-триггерах. Для чего организуют D- вход (рис. 5.15)

Рисунок 5.15 – Регистр сдвига на JK - триггерах

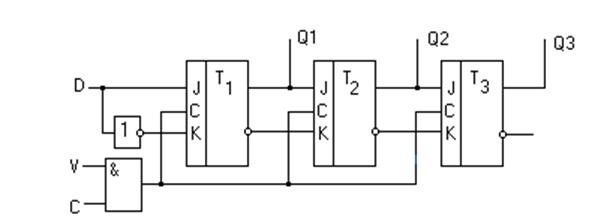

Так как цепь синхронизации является общей для всего блока (или узла), а микрооперацию сдвига требуется выполнить не всегда, то делают дополнительный вход через конъюнктор (рис. 5.16). При V=1 сдвиг будет выполнен по синхросигналу. При V=0 сдвига не будет.

Рисунок 5.16 – Регистр сдвига на JK – триггерах c конъюнктором

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.