Синтезируем шифратор. Для этого запишем систему собственных функций

,

,

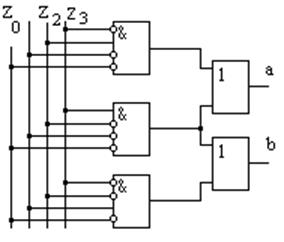

по которой составим схему (рис. 3.8):

Рисунок 3.8 – Схема шифратора при n = 2

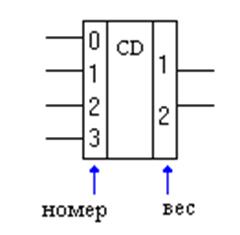

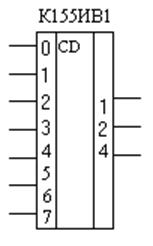

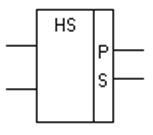

Условное обозначение шифратора и пример микросхемы приведены на рис. 3.9

Рисунок 3.9 – Условное обозначение шифратора

Шифраторы имеются во многих сериях микросхем, например, К555ИВ3, 533ИВ2 и др.

3.2 Мультиплексор и демультиплексор

Мультиплексор (коммутатор) это многовходовая комбинационная схема служит для коммутации одного из 2n информационных входов на выход под действием n управляющих (адресных) сигналов.

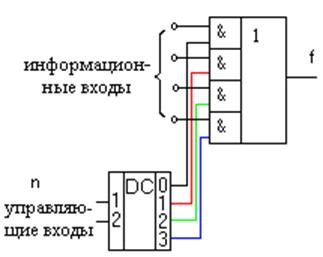

Составим схему мультиплексора при n = 2 (рис. 3.10).

Рисунок 3.10 – Схема мультиплексора

Мультиплексор реализует дизъюнкцию элементарных конъюнкций и является универсальным устройством.

,

,

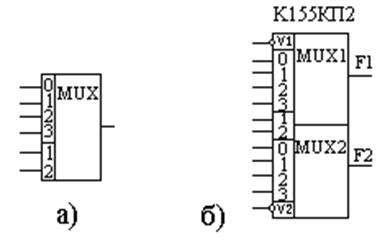

где Zi – информационный сигнал, Xi – сигналы с выхода декодера. Условное обозначение мультиплексора (рис. 3.11 а ):

Рисунок 3.11 – Условное обозначение и пример микросхемы

Мультиплексоры выпускаются как отдельные микросхемы. Например, сдвоенный четырёхканальный мультиплексор К155КП2 (рис.3.11 б), который имеет общий декодер на оба канала.

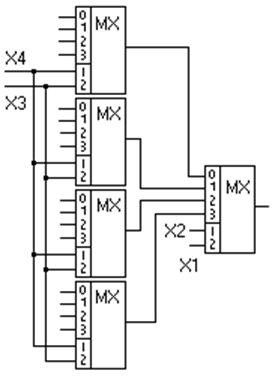

Промышленностью выпускаются мультиплексоры с числом адресных входов 2, 3, 4. Если этого недостаточно, то используют их каскадное включение.

Пусть требуется создать 16 – канальный мультиплексор

из 4 – канальных. Значит адрес должен быть четырёхразрядным Х![]() Х

Х![]() Х

Х![]() Х

Х![]() ( 2

( 2![]() = 16 ). Этот адрес подаётся на входы

декодеров определённым образом (рис. 3.12)

= 16 ). Этот адрес подаётся на входы

декодеров определённым образом (рис. 3.12)

Рисунок 3.12 – Мультиплексор на 16 каналов (16 ![]() 1)

1)

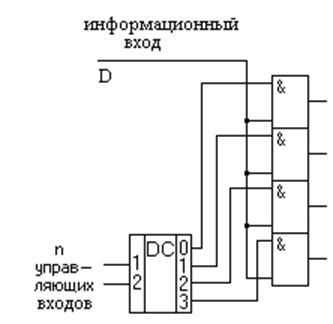

Демультиплексор

Выполняет функцию обратную мультиплексору, то есть коммутирует один информационный вход на один из 2n выходов под действием n управляющих (адресных) сигналов. Составим схему демультиплексора при n = 2 (рис. 3.13).

Рисунок 3.13 – Демультиплексор на 4 канала

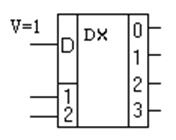

Очевидно, что если на информационный вход (D) подать 1, то это будет дешифратор в чистом виде. Вход D можно использовать как клапан (V) (рис.3.14)

Рисунок 3.14 – Обозначение демультиплексора

Микросхема так и называется дешифратор – демультиплексор. Например, ИМС КР531ИД14.

3.3 Сумматоры

Сумматор – это узел ЭВМ, предназначенный для сложения кодов двоичных чисел. Сумматоры делятся на последовательные (накапливающие) и параллельные (комбинационные). Накапливающие сумматоры имеют низкое быстродействие, поэтому они рассматриваться не будут. В комбинационных сумматорах слагаемые поступают на входы одновременно, а на выходе получается код суммы. После снятия слагаемых результат пропадает. Эти устройства не обладают памятью и строятся на логических элементах.

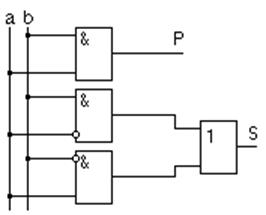

Составим таблицу истинности устройства для сложения двух одноразрядных чисел a и b (рис. 3.15)

|

№ |

a |

b |

p |

s |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

2 |

1 |

0 |

0 |

1 |

|

3 |

1 |

1 |

1 |

0 |

Рисунок 3.15 – Таблица истинности для сложения двух цифр

Здесь р – перенос в старший разряд, s – значение суммы. Устройство, реализующее эту таблицу истинности, называют двоичным полусумматором. Его можно синтезировать по ФАЛ для каждого из выходов

Составим схему на произвольных элементах (рис. 3.16)

Рисунок 3.16 – Схемная реализация и условное обозначение

полусумматора

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.