|

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

|

1-8 |

А0-А7 |

Вход/выход |

Информационная шина |

|

9 |

OE |

Вход |

Разрешение передачи (управление 3-им состоянием) |

|

10 |

GND |

- |

Общий |

|

11 |

T |

Вход |

Выбор направления передачи |

|

12-19 |

В7-В0 |

Выход/вход |

Информационная шина |

|

20 |

Ucc |

- |

Напряжение питания +5В |

В качестве системного дешифратора используется дешифратор/демультиплексор 3X8 1533ИД7[3]. На его входы DI1, DI2 и DI4 поступают сигналы адреса А13-А15, соответственно. На разрешающий вход С1 поступает сигнал PDEN. С выходов дешифратора на входы выборки кристалла микросхем ОЗУ, ПЗУ, внешних и интерфейсных устройств поступают сигналы CS0-CS7.

Сигнал |

Адреса |

Выбираемая микросхема |

|

CS0 |

0000 |

07FF |

ОЗУ |

CS1 |

2000 |

2001 |

Контроллер прерываний |

CS2 |

4000 |

4003 |

Таймер |

CS3 |

6000 |

6003 |

|

CS4 |

8000 |

8003 |

|

CS5 |

A000 |

A003 |

АЦП |

CS6 |

C000 |

C000 |

|

CS7 |

E000 |

FFFF |

ПЗУ |

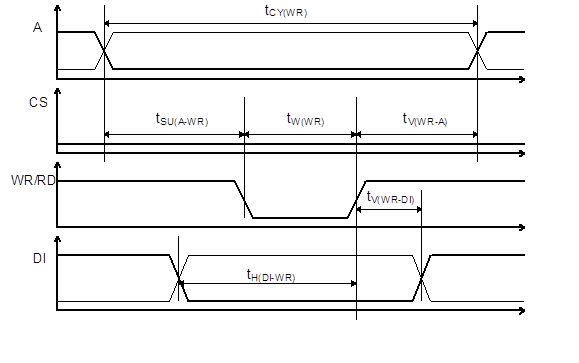

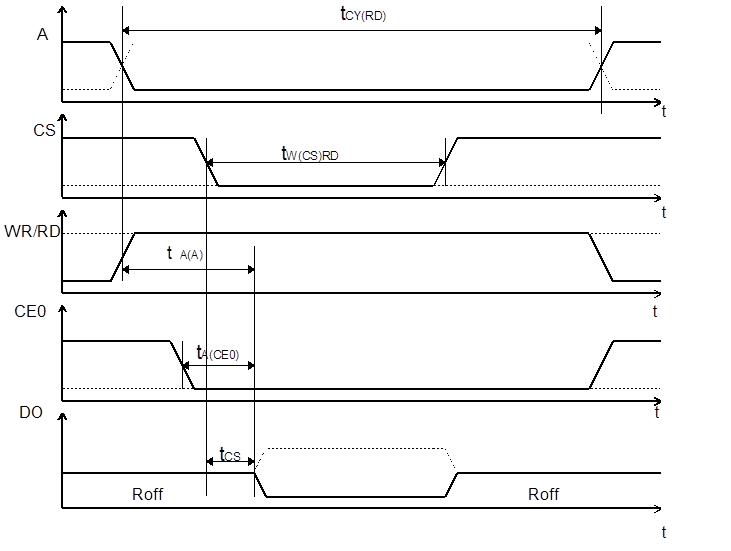

Под ОЗУ для решения нашей задачи требуется около 40-60 байт, поэтому используется микросхема ОЗУ КР537РУ10[4]. Ее информационная емкость составляет 2Кбайт, что приблизительно в 50 раз больше, согласно заданию, нужной емкости. Временные диаграммы микросхемы представлены на рис. 2.2 и рис. 2.3.

а.)

б.)

Рис. 2.2. Временные диаграммы работы микросхемы КР537РУ10:

а. режим записи с постоянноя выборкой (CS=const);

б. режим записи с импульсной выборкой

Рис. 2.3. Временные диаграммы работы микросхемы КР537РУ10 в режиме считывания

Наборы управляющих сигналов, подаваемые на входы ОЗУ и соответствующие различным режимам работы ОЗУ представлены в табл. 2.13.

Таблица 2.13

|

CS |

CE0 |

WR/RD |

A0-A10 |

DIO0-DIO7 |

Режим работы |

|

H |

X |

X |

X |

Roff |

Хранение |

|

L |

X |

L |

A |

L |

Запись 0 |

|

L |

X |

L |

A |

H |

Запись 1 |

|

L |

L |

H |

A |

Данные в прямом коде |

Считывание |

|

L |

H |

H |

A |

Roff |

Запрет выхода |

Динамические параметры микросхемы КР537РУ10 приведены в табл. 2.14.

Таблица 2.14

|

Параметры |

Значения параметров |

||

|

мин. |

макс. |

||

|

Время выборки адреса, tA(A), нс |

- |

220 |

|

|

Время выбора, tCS, нс |

- |

220 |

|

|

Время выборки сигнала разрешения по выходу, tA(CEC), нс |

- |

150 |

|

|

Время установления сигнала CS относительно адреса,tSU(A-CS), нс |

30 |

- |

|

|

Время установления сигнала записи относительно адреса, tSU(A-WR), нс |

30 |

- |

|

|

Время сохранения входных данных после сигнала записи, tV(WR-DI), нс |

30 |

- |

|

|

Время сохранения входных данных после сигнала CS,tV(CS-DI), нс |

30 |

- |

|

|

Время удержания сигнала записи относительно входных данных, tH(DI-WR), нс |

160 |

- |

|

|

Время удержания сигнала CS относительно входных данных, tH(DI-CS), нс |

160 |

- |

|

|

Длительность сигнала CS в режиме считывания, tW(CS)RD, нс |

220 |

- |

|

|

Длительность сигнала CS в режиме записи, tW(CS)WR, нс |

160 |

- |

|

|

Длительность сигнала записи, tW(WR), нс |

160 |

- |

|

|

Время сохранения адреса после сигнала CS, tV(CS-A), нс |

30 |

- |

|

|

Время сохранения адреса после WR, tV(WR-A), нс |

30 |

- |

|

|

Время цикла записи, tCY(WR), нс |

220 |

- |

|

|

Время цикла считывания, tCY(RD), нс |

220 |

- |

|

|

Входная емкость, CI, пФ |

- |

8 |

|

|

Выходная емкость, CO, пФ |

- |

14 |

|

|

Емкость нагрузки, CL, пФ |

- |

50 |

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.