Рис. 10. Функциональная схема буфера данных BFD. |

Таблица 4

|

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

|

1- 8 |

D0-D7 |

Вход |

Информационная шина |

|

9 |

OE |

Вход |

Разрешение передачи (управление 3-им состоянием) |

|

10 |

GND |

- |

Общий |

|

11 |

STB |

Вход |

Стробирующий сигнал |

|

12-19 |

Q7-Q0 |

Выход |

Информационная шина |

|

20 |

UCC |

- |

Напряжение питания +5В |

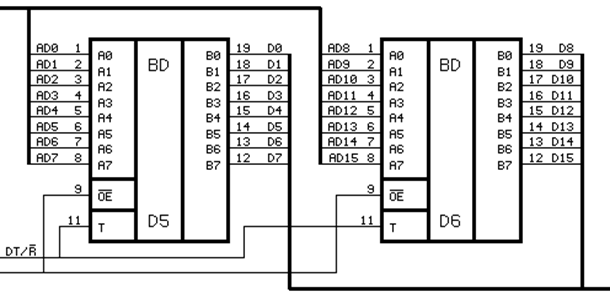

Помимо регистра адреса, сигналы AD0 - AD15 поступают на буфер данных BFD. В качестве шинного формирователя BF использована микросхема КР580ВА86. Поскольку шина данных 16-битная, то необходимо две таких микросхемы. Назначение выводов микросхемы указано в табл. 5. Схема подключения показана на рис. 10. На входы Т подается сигнал DT/R, с контроллера системной шины, а на вход OE подается сигнал со схемы ИЛИ-НЕ на которую в свою очередь подаются сигналы DEN с контроллера системной шины и DE с контроллера прерываний.

Таблица 5

|

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

|

1-8 |

А0-А7 |

Вход/выход |

Информационная шина |

|

9 |

OE |

Вход |

Разрешение передачи (управление 3-им состоянием) |

|

10 |

GND |

- |

Общий |

|

11 |

T |

Вход |

Выбор направления передачи |

|

12-19 |

В7-В0 |

Выход/вход |

Информационная шина |

|

20 |

UCC |

- |

Напряжение питания +5В |

Сигналы адреса, выходящие с регистра адреса, поступают на системный дешифратор DCS. В качестве которого используется дешифратор/демультиплексор 3´8 1533ИД7. На его входы 1, 2, 3 поступают сигналы адреса А3-А5, соответственно. На разрешающие входы С1, С2, С3 поступают сигналы A6, A7 и A7 соответственно. С выходов дешифратора сигналы C4-C11 поступают на входы выборки микросхем внешних и интерфейсных устройств. В таблице 6 приведены адреса распределяемые системным дешифратором для внешних устройств. Схема подключения показана на рис. 11.

Принципиальная схема МПМ показана на рис. 12.

Таблица 6

|

Сигнал |

Адреса |

Выбираемая микросхема |

|

|

C4 |

40 |

41 |

Контролер прерываний (PIC) |

|

C5 |

48 |

49 |

Контроллер клавиатуры / дисплея (IOP) |

|

C6 |

50 |

53 |

Параллельный интерфейс (IOP) |

|

C7 |

58 |

5F |

АЦП (ADC) CS |

|

C8 |

60 |

67 |

Защелкивание адреса на АЦП сигнал ALE |

|

C9 |

68 |

- |

Не используется |

|

C10 |

70 |

- |

Не используется |

|

C11 |

78 |

- |

Не используется |

Так как шина данных процессора – 16-разрядная, разобьем память на 2 банка – для хранения младшего и старшего байтов соответственно.

Под ОЗУ для решения нашей задачи требуется около 200 байт, с учетом запаса можно взять 4Кбайта, поэтому для каждого банка ОЗУ используется 8-разрядная микросхема КР537РУ10. Ее информационная емкость 2Кбайт. Таким образом общий объем ОЗУ – 4Кбайт.

|

Рис. 11. Схема подключения DCS. |

|

Рис. 12. Принципиальная схема МПМ. |

Временные диаграммы микросхемы представлены на рис. 13 и рис. 14

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.