Рис. 4.13

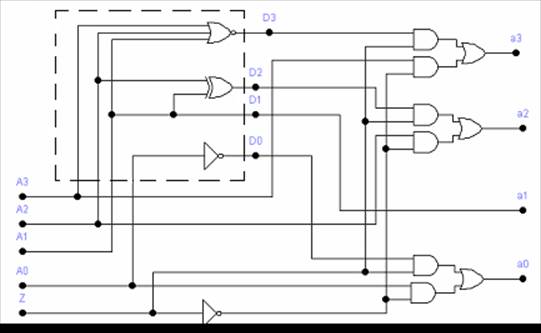

Рис. 4.14. Схема управляемого преобразователя кода 8-4-2-1

в дополнение до 9 и его графическое обозначение

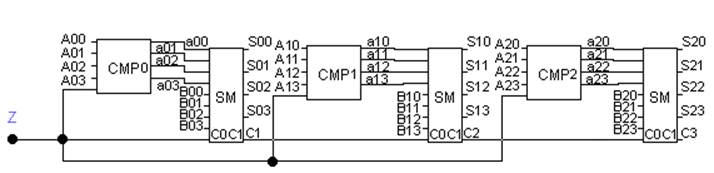

Рис. 4.15

Изложенный принцип работы сумматора–вычитателя проиллюстрирован на трех примерах.

Пример 1. Суммирование трехразрядных положительных десятичных чисел

(В10+А10)

х102 х101 x100 — веса десятичных разрядов

8421 8421 8421 —веса двоичных разрядов

1 1 0 —перенос

548 +0101 +0100 +1000 — тетрады операнда В в коде 8-4-2-1

![]() +278 0010 0111 1000

— тетрады

операнда А в коде 8-4-2-1

+278 0010 0111 1000

— тетрады

операнда А в коде 8-4-2-1

826 1000 +1100 1 +0000 — сумма тетрад

0110 0110 — коррекция

![]() 1000 1 0010 1 0110 — суммы в коде 8-4-2-1

1000 1 0010 1 0110 — суммы в коде 8-4-2-1

8 2 6 — сумма в десятичной системе счисления

Пример 2. Вычитание трехразрядных положительных десятичных чисел

(B10-A10>0).

х102 х 101 х100 — веса десятичных разрядов

8421 8421 8421 —веса двоичных разрядов

0 1 1 —перенос

548 + 0101 +0100 +1000 — тетрады операнда Bв прямом коде

+278 + 0111 + 0010 + 0001 — тетрады операнда А в доп. коде до 9

270 1100 0111 1010 — сумма тетрад с учетом переноса

+ 0110 +0110 — коррекция перенос 1 0010 0111 1 0000 — сумма в коде 8-4-2-1

в следующий 2 7 0 — сумма в десятичной системе счисления разряд

Пример 3. Вычитание трехразрядных положительных десятичных чисел

(В10-А10<0).

х102 х101 х100 — веса десятичных разрядов

8421 8421 8421 — веса двоичных разрядов

+ 1 + 1 + 1 —перенос

278 0010 +0111 1000 —тетрады операнда B в прямом коде 8-4-2-1

+548 0100 0101 0001 —тетрады операнда А в доп. коде до 9

730 0111 1101 1010 — сумма тетрад

0110 0110 — коррекция перенос 0 0111 1 0011 1 0000 — разряды суммы в дополниельном коде в следующий 7 3 0 — дополнение до 1000 дает – 270 разряд

1. Приведите несколько вариантов схемной реализации функции суммы по модулю два для двух аргументов на различных элементах: а) И, ИЛИ, НЕ; б) И‑НЕ; в) ИЛИ‑НЕ; г) И‑ИЛИ‑НЕ.

2. Постройте таблицу истинности для функций суммы S переноса p одноразрядного сумматора. После их минимизации реализуйте схему на элементах И‑НЕ.

3. Как получено выражение для суммы (4), не требующее инверсных значений входных переменных? Реализуйте схему этой функции на элементах И‑ИЛИ‑НЕ.

4. Постройте схему одноразрядного сумматора на основе готовых полусумматоров. Чем отличается полусумматор от полного сумматора?

5. Какие функции выполняет схема рис. 4.5?

6. Объясните принципы организации сумматоров с групповым переносом. Попробуйте создать схему сумматора с параллельным переносом заданной разрядности на любых известных вам элементах.

7. Поясните работу двоичного сумматора–вычитателя.

8. Расскажите о возможных режимах работы микросхемы четырехразрядного АЛУ 74181 (К155ИП3).

9. Поясните работу одноразрядного двоично‑десятичного сумматора. Как и почему осуществляется в нем десятичная коррекция?

10. Поясните работу одноразрядного двоично‑десятичного сумматора без коррекции результата.

11. Сравните двоично‑десятичные сумматоры п. 9 и п. 10.

12. Поясните работу одноразрядного двоично‑десятичного сумматора–вычитателя.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.