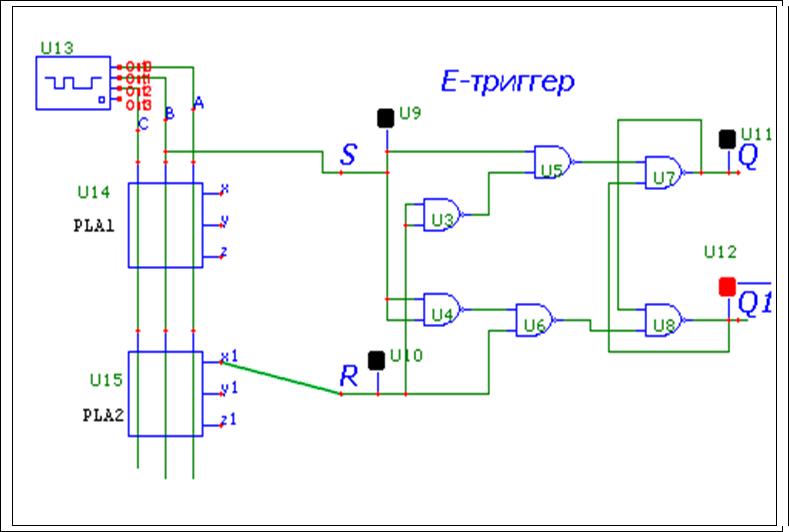

2. Собрать из логических элементов И – НЕ простейшую схему Е-триггера (рис. 2). Получить для этой схемы таблицу переключений триггера, пользуясь методикой, приведенной выше. Убедиться, что запретные сочетания «00» и «11» неустойчивы и автоматически исключаются, а устойчивые состояния выходов всегда инверсны.

3.![]() Реализовать схему JK-тригтера (рис. 3) из состава

логических элементов наборного поля. Пользуясь приведенной выше

методикой, составить таблицу

переключений JK-триггера. Определить, имеются ли у этого

триггера запрещенные комбинации входных сигналов.

Реализовать схему JK-тригтера (рис. 3) из состава

логических элементов наборного поля. Пользуясь приведенной выше

методикой, составить таблицу

переключений JK-триггера. Определить, имеются ли у этого

триггера запрещенные комбинации входных сигналов.

4. Собрать схему RS-триггера с инверсными входами согласно рис. 4 в программе «MC 9 DEMO», составить таблицу переключений триггера. Схема RS -триггера с инверсными входами в файле «SOLRS inv vx».

Рис. 4 5. Собрать схему Е-триггера согласно рис. 5 в среде «MC 9 DEMO», получить таблицу переключений триггера. Схема Е-триггера собрана в файле «SOL Е триггер».

Рис. 5

6. Войти в меню File, выбрать файл «SOL E тргг урв» с принципиальной схемой Е-триггера, “Stim4 Generators” (рис. 6) в среде «МС9 DEMO». Составить таблицу переключений триггера для различных комбинаций входных сигналов, подключая входы Е-триггера S и R к выходам A, B, C, x, y, z, x1, y1, z1.

Рис. 6

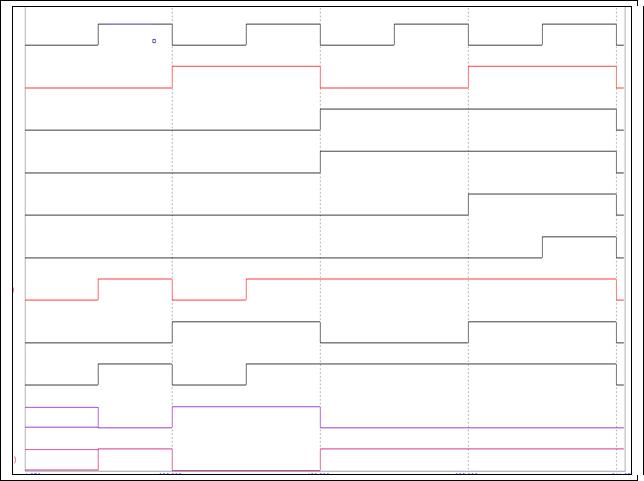

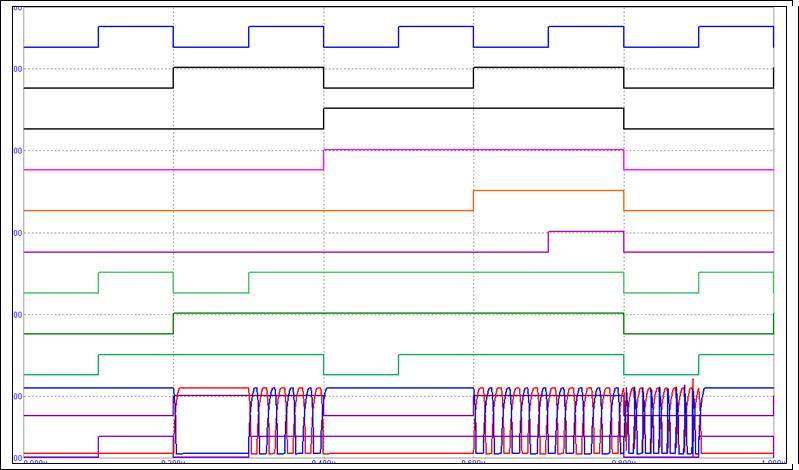

На рис. 7 приведены временные диаграммы сигналов на выходах A, B, C, x, y, z, x1, y1, z1, а также выходах Е-триггера Qи Q1.

Рис. 7

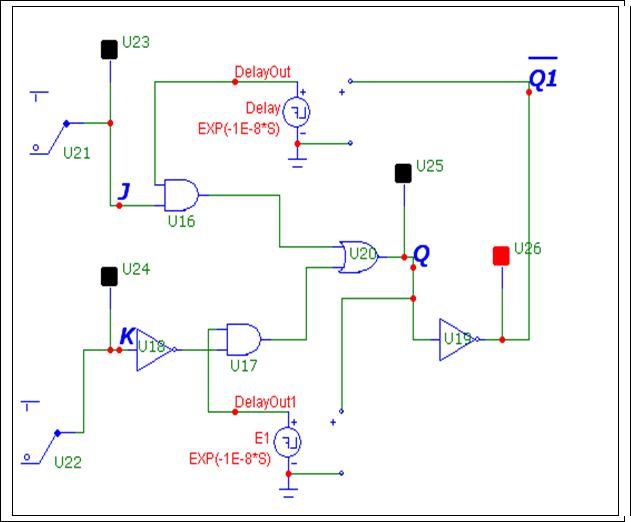

7. Войти в меню File, выбрать файл «SOL JK зад TR» с принципиальной схемой JK-триггера в программе моделирования «MC 9 DEMO», составить таблицу переключений триггера. На рис. 8 представлена схема JK-триггера, реализованная в соответствии с формулой (2).

Рис. 8

Введение в цепях обратной связи JK-триггера элементов задержки (Delay: LF) является необходимым условием нормальной работы триггера в случае одномоментного поступления запрещенных сочетаний входных сигналов J=K=1.

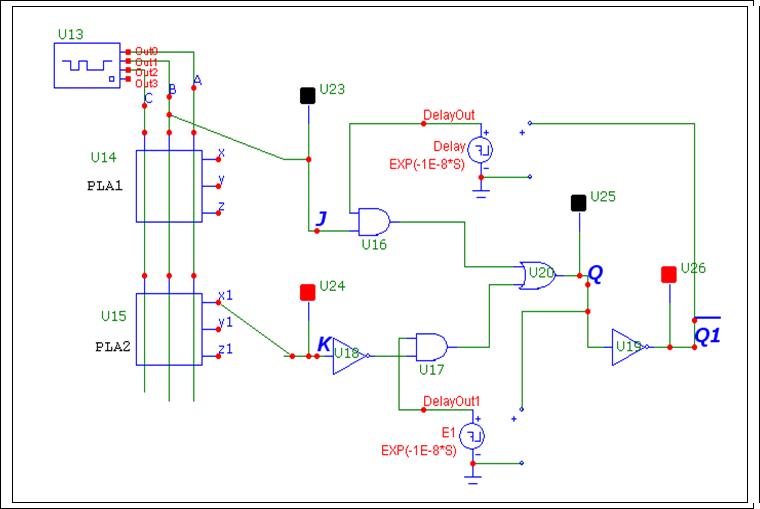

Рис. 9

8. Войти в меню File, выбрать файл «SOL JK PLA» с принципиальной схемой JK-триггера, входные сигналы на который подаются с программируемых логических матриц PLA1 b PLA2 (рис. 9). Провести моделирование для различных комбинаций входных сигналов, подключая входы JK-триггера к выходам A, B, C, x, y, z, x1, y1, z1 “Stim4 Generators”, “PLA1” и “PLA2”.

Рис. 10

9. На рис. 10 приведены временные диаграммы сигналов на выходах A, B, C, x, y, z, x1, y1, z1, а также выходах Е-триггера Qи Q1.

4. Содержание отчета

1. Схемы исследуемых асинхронных триггеров.

2. Таблицы переключений.

3. Временные диаграммы.

4. Выводы по работе.

Литература [1], с. 32…35; [5], с. 150...178

Работа 5

Исследование синхронных триггеров

1. Цель работы

Целью работы является:

1. Исследование на стенде УМ-11 способов синтеза синхронных потенциальных триггеров на микросхемах средней степени интеграции и составление таблицы переключений триггеров для различных комбинаций входных сигналов.

2. Исследование на ПК работы синхронных RSC-триггера и D-триггера.

2. Основные теоретические положения

В процессе подготовки к лабораторной работе студентам необходимо изучить раздел 4 учебного пособия [1].

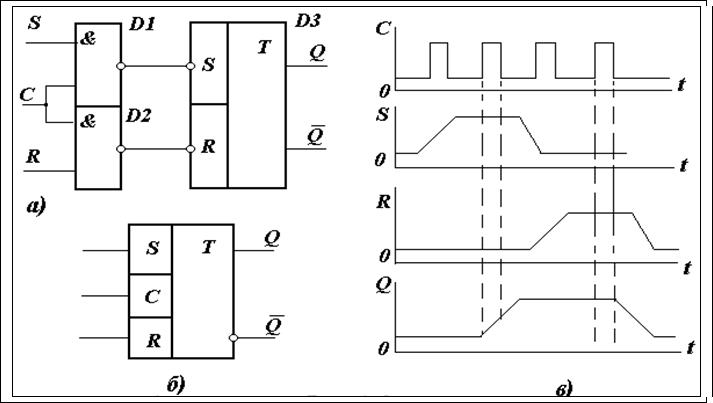

Синхронный RS-триггер (RSC-триггер) реализуется на асинхронном RS-триггере с инверсными входами (элемент D3 на рис. 1, а).

Рис. 1

Управляющие сигналы на каждый из входов триггера подаются через элементы И – НЕ (элементы D1, D2 на рис. 1, а). Условное графическое изображение триггера показано на рис. 1, б, а временные диаграммы – на рис. 1, в.

Элемент D1 обеспечивает совпадение синхроимпульсов С и установочных сигналов S , т. е. временное стробирование сигналов S, а элемент D2 стробирует по времени сигналы R.

![]()

![]() D-триггер (триггер задержки) . В синхронных триггерах в промежутке между

синхроимпульсами выходные напряжения не изменяются. Это позволяет создать на

основе синхронизируемых RS – триггеров триггеры задержки – D-триггеры.

D-триггер (триггер задержки) . В синхронных триггерах в промежутке между

синхроимпульсами выходные напряжения не изменяются. Это позволяет создать на

основе синхронизируемых RS – триггеров триггеры задержки – D-триггеры.

Рис. 3

Рис. 2

На рис. 2 изображена схема D-триггера, в основе работы которого лежит то, что он принимает информацию по входу D.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.