Комбинационное устройство – это логическая схема с mвходами (m³1 ) и nвыходами (n³1), у которой состояния выходов лишь определяются состояниями входов в тот же момент времени. Рассмотрим следующие комбинационные устройства: полусумматоры, сумматоры, неравнозначности и равнозначности.

![]() Полусумматором называется устройство для сложения двух

одноразрядных двоичных чисел. В результате сложения в общем случае наряду с

суммой может получиться перенос, т. е. это устройство имеет два входа и два

выхода. Таблица истинности представлена в виде табл. 1, Знаки «штрих», которые

стоят около выходов S¢ и P¢, ставятся для отличия полусумматора от полного сумматора.

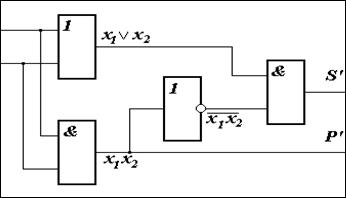

По табл. 1 можно составить структурные формулы (1) и (2) и соответственно

принципиальную схему полусумматора (рис. 1).

Полусумматором называется устройство для сложения двух

одноразрядных двоичных чисел. В результате сложения в общем случае наряду с

суммой может получиться перенос, т. е. это устройство имеет два входа и два

выхода. Таблица истинности представлена в виде табл. 1, Знаки «штрих», которые

стоят около выходов S¢ и P¢, ставятся для отличия полусумматора от полного сумматора.

По табл. 1 можно составить структурные формулы (1) и (2) и соответственно

принципиальную схему полусумматора (рис. 1).

х1

х2

Рис. 1

![]() (1)

(1)

(2)

(2)

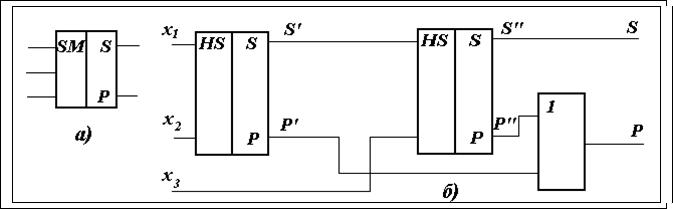

Полный сумматор – устройство, предназначенное для сложения трех одноразрядных двоичных чисел x1, x2 , x3 .Эта задача возникает при поразрядном сложении двоичных чисел, когда третье слагаемое переносится из предыдущего младшего разряда. Условное графическое изображение устройства представлено на рис. 2, а, а принципиальная схема – на рис. 2, б.

Рис. 2

Как следует из рис. 2, б, полный сумматор строится из двух полусумматоров и одного элемента, выполняющего операцию дизъюнкции двух переносов, возникающих в каждом полусумматоре. Поэтому полный сумматор также имеет два выхода: S– сумму и P– перенос.

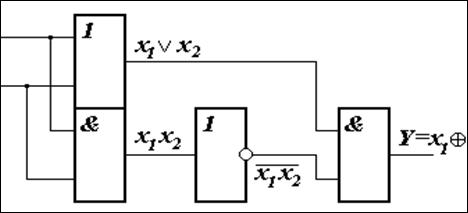

Устройство неравнозначности – это устройство с двумя входами x1 , x2и одним выходом Y, реализующим логическую функцию, называемую ИСКЛЮЧАЮЩЕЕ ИЛИ: Y = 1 только при несовпадении информационных значений входных сигналов.

Условное изображение этого объекта на функциональных схемах представлено на рис. 3. Эта схема имеет специальное обозначение и называется . Рис. 3 «сумматор по модулю 2»

![]() (3)

(3)

х1

х2

Рис. 4

Логическая схема, выполняющая эту функцию, представлена на рис. 4. Для этой функции существует ряд дополнительных тождеств, которые приведены в [5].

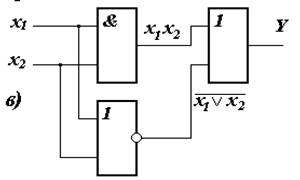

Устройство равнозначности – устройство с двумя входами x1 и x2 и одним выходом Y. Сигнал «1» на выходе устройства появится

только при совпадении информационных значений входных сигналов.

Устройство равнозначности – устройство с двумя входами x1 и x2 и одним выходом Y. Сигнал «1» на выходе устройства появится

только при совпадении информационных значений входных сигналов.

Принципиальная схема устройства равнозначности представлена на рис. 5.

Рис. 5

3. Описание лабораторного макета

Лабораторная установка выполнена на базе учебного макета УМ-21 и состоит из следующих блоков: восьмиразрядного арифметико-логического устройства (АЛУ); сумматора на два восьмиразрядных числа; тумблерных и регистровых блоков памяти операндов А и В; выходного регистра информации - С; мультиплексора (MX) 4x1; запоминающего устройства (DS); счетчика адреса микрокоманд; триггера признаков D-типа; генератора синхроимпульсов и счетчика циклов; блоков управления в аппаратном и микропрограммном режимах.

В данной работе используется только аппаратный режим управления блоками установки. Принципиальные схемы блоков, входящих в макет, приведены на лицевой панели макета. Съемный блок передней панели необходимо установить стороной «Аппаратное управление», т. е. для исследования сумматора (платы 1, 2,3,4 включены, а 5 и 6 выключены на задней стенке макета).

Регистр А хранит восьмиразрядную информацию, которая может быть в него занесена с тумблерного регистра автоматически. Он выполнен на интегральных микросхемах К155ТМ8 (четыре D-триггера в одном корпусе). Логика управления на входе позволяет использовать прямое и инверсное значения операнда А (за счет сигнала VRGA). Записанная информация индицируется светодиодами поразрядно.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.