Демультиплексоры выполняют функцию, обратную функции мультиплексора, т. е. коммутируют один входной сигнал на 2mвыходов.

И мультиплексоры, и демультиплексоры – это коммутаторы логических сигналов. Демультиплексоры иногда называются распределителями. На передающей стороне используются мультиплексоры, а на приемной – демультиплексоры, т. е. совместное использование этих устройств позволяет осуществить временное разделение (уплотнение) каналов. Следует отметить, что в технической литературе встречаются обозначения мультиплексоров MX и MS.

Демультиплексор обычно обозначается тем же символом, что и дешифратор (декодер), т. е. DC. Иногда пишется и символ, обозначающий, на сколько выходов коммутируется входной сигнал.

Логическое выражение, связывающее выходные переменные yi с входными mi и переменной Bна информационном входе, можно представить выражением [1]

где mi = A1 …Ap – полные правильные конъюнкции, т. е.

минтермы на управляющих входах;

где mi = A1 …Ap – полные правильные конъюнкции, т. е.

минтермы на управляющих входах;

i = 0, 1 … 2p – 1;

p– число управляющих переменных.

Устройство сравнения кодов (цифровой компаратор)

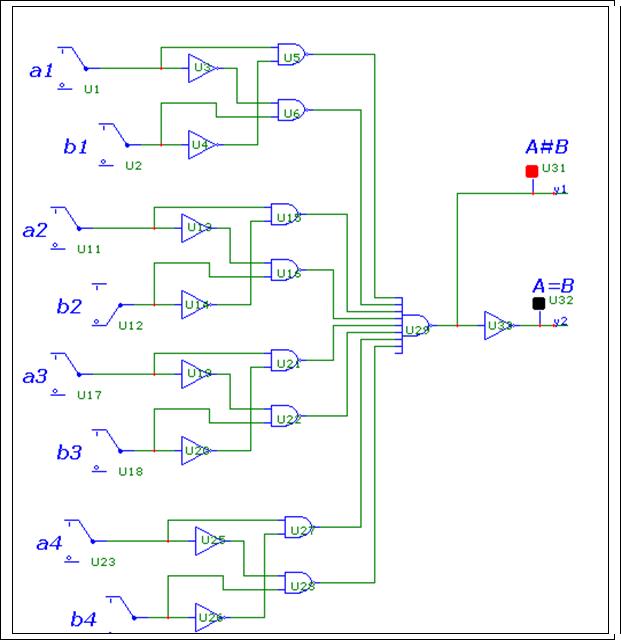

В цифровой технике эти устройства применяются в виде схем сравнения двух чисел (слов), двух n-разрядных двоичных кодов A(an, an-1 … a1) и B (bn, bn-1 …b1), где ai, bi – двоичные переменные «0» или «1».

В результате сравнения кодов чаще всего требуется установить факт равенства A = B, т. е. равенства ai , bi для всех i = 1, 2 … n , либо факт неравенства A¹B – если хотя бы в одном k-м разряде ak ¹bk.

Иногда факта неравенства недостаточно и требуется установить знак неравенства, т. е., что, действительно, имеет место A>Bили A<B.

Равнозначность разрядов aiи bi определяется схемой равнозначности, истинностью функции

Поэтому равенство кодов определяется истинностью конъюнкции всех fi.

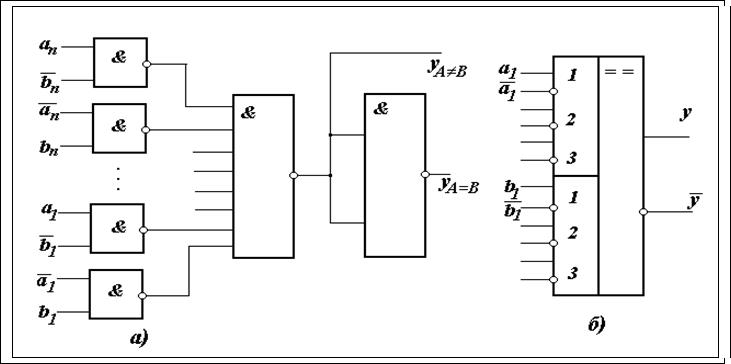

Цифровой компаратор можно получить в различных логических базисах. В базисе И – НЕ согласно [5] цифровой компаратор имеет вид

.

По последней структурной формуле составлена логическая схема, показанная на рис. 2, а. Условное графическое изображение устройства сравнения кодов представлено на рис. 2, б.

Рис. 2

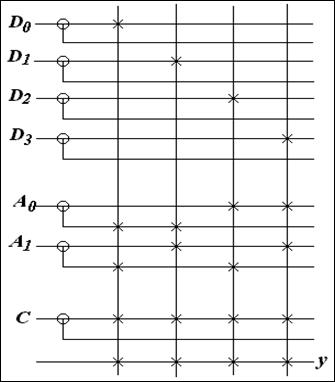

Мультиплексор и демультиплексор на ПЛМ. Схема мультиплексора на четыре входа (D3, D2, D1, D0) показана на рис. 3. На этом рисунке А1, А0– адресные входы; С – вход для подачи сигнала разрешения выдачи; y– выход.

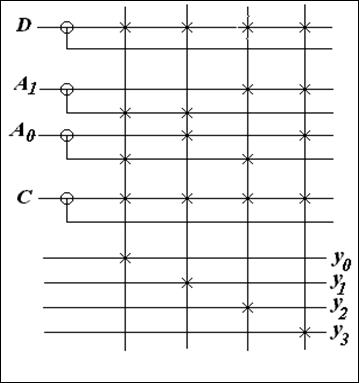

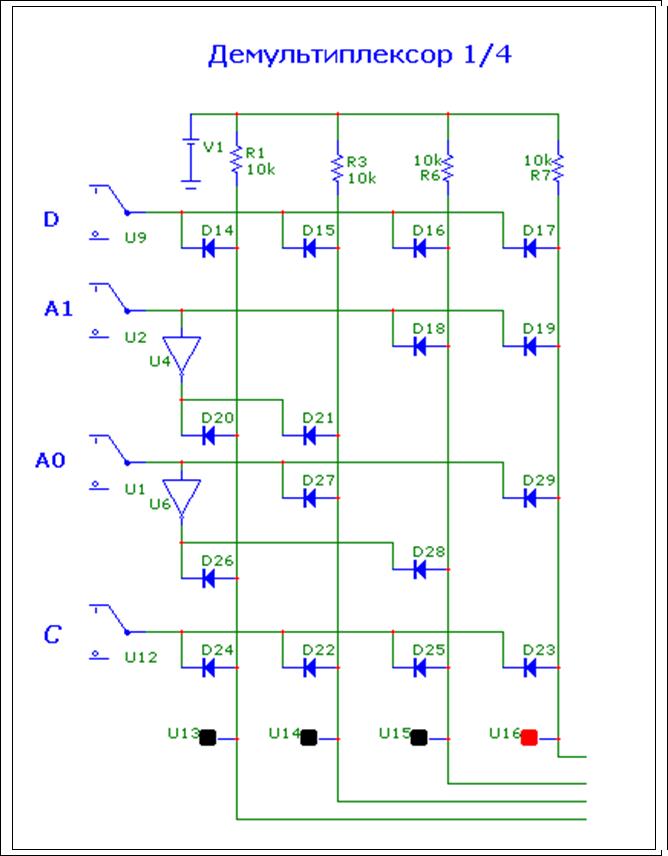

На рис. 4 приведена схема демультиплексора на четыре выхода (y3, y2, y1,y0).На этом рисунке D– вход; А1, А0 – адресные входы; С – вход сигнала разрешения выдачи информации.

Рис. 3 Рис. 4

Порядок выполнения работы

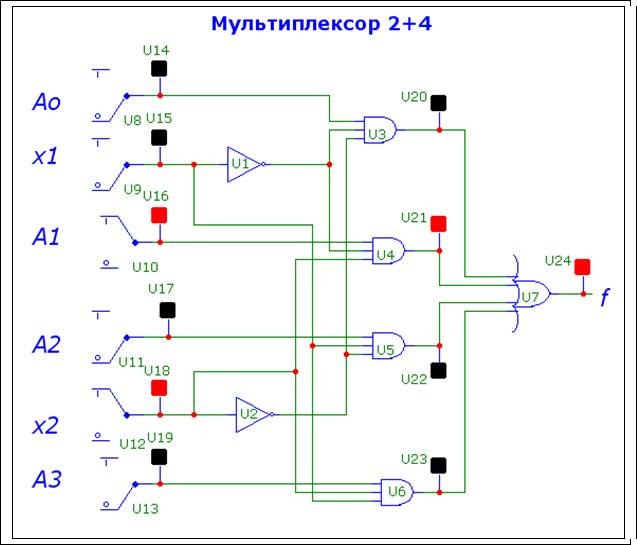

1. Войти в меню File, в появившемся окне выбрать файл «SО Млтп 2 4» c принципиальной схемой (рис. 5) мультиплексора 2+22 в программе «МС9 DEMO» и провести его исследование.

Рис. 5

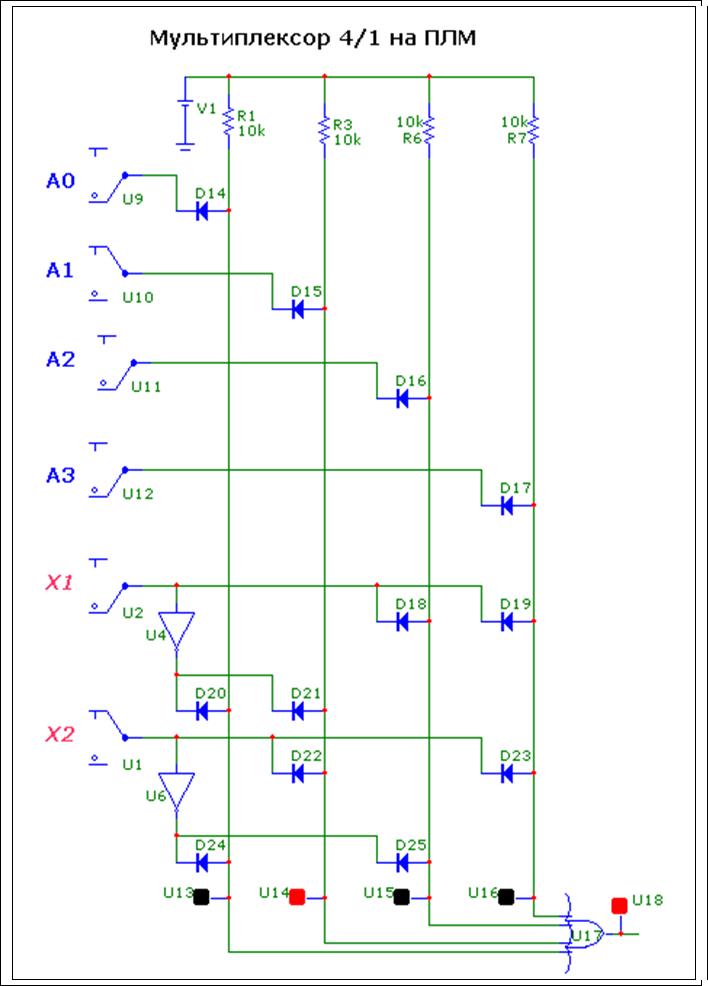

2. Войти в меню File, выбрать файл «SO Млтп PLM» c принципиальной схемой (рис. 6) мультиплексора 2+22, выполненной в программе «МС9 DEMO» по схеме программируемой логической матрицы. Провести исследование данной схемы.

Рис. 6

3. Войти в меню File, выбрать файл «SO 1 4 Дмлт» c принципиальной схемой (рис. 7) демультиплексора 1/4, выполненной в программе «МС9 DEMO». Провести исследование данной схемы.

Рис. 7

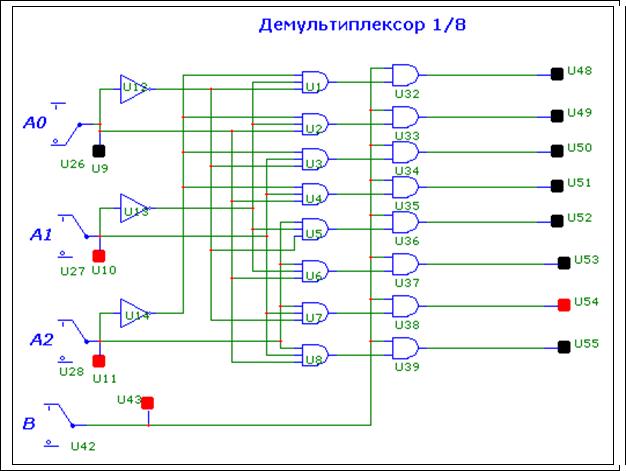

4. Войти в меню File, выбрать файл «SO Дмлт 1 8» c принципиальной схемой (рис. 8) демультиплексора 1/8, выполненной в программе «МС9 DEMO». Провести исследование данной схемы.

5. Войти в меню File, выбрать файл «SO Компртр 4р» c принципиальной схемой (рис. 9) четырехразрядного компаратора, выполненной в программе «МС9 DEMO». Провести исследование данной схемы.

Рис. 8

Рис. 9

4. Содержание отчета

1. Структурные схемы мультиплексоров, демультиплексоров, компараторов.

2. Принципиальные схемы исследуемых комбинационныхустройств, выполненные в среде «МС9 DEMO».

3. Таблицы истинности комбинационныхустройств.

4. Выводы.

Литература: [1], с. 29...32; [4], с. 61… 64; [5], с. 149 ...154

Работа 4

Исследование асинхронных триггеров (на стенде и ПК)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.