|

Адрес |

Код |

Метка |

Мнемокод |

Комментарий |

|

0800 |

31000В |

LXI SP, 0B00 |

SP ← адрес вершины стека |

|

|

0803 |

CD0780 |

CALL STD |

Идти к ПП STD |

|

|

0806 |

76 |

HLT |

Стоп |

|

|

0801 |

F5 |

STD |

PUSH PSW |

Запись в стек слова состояния |

|

… |

В программе указывается начальный адрес каждой команды, но при этом понимается, что в зависимости от длины (одно-, двух- или трехбайтная) команды будут занимать от одной до трех последовательных ячеек. При такой записи в левом столбце указываются лишь начальные адреса команд в программе. Столбец «Метка» появляется в программе в том случае, если в программе осуществляются условные или безусловные переходы.

Режимы адресации

· Неявный (регистровый) – работает только с регистрами

· Непосредственный – загружает число в аккумулятор. MVI A, 5B A←5Bh

· Прямой – обмен данными между регистрами и ячейкой памяти, причем адрес ячейки памяти, с которой производятся определенные действия, указывается непосредственно в команде, которая эти действия производит. LDA 0820 A←M0820; STA 0820 M0820←A.

· Косвенный – позволяет обмениваться данными между ячейкой памяти и регистром, но при этом адрес ячейки, с которой предполагается произвести какие-либо действия, предварительно помещается в одну из трех регистровых пар Далее, при необходимости обратитесь к ячейке памяти, адрес которой записан в регистровой паре, используют соответствующие команды. Косвенный способ адресации позволяет экономить место в программе, т.к. команды в этом случае становятся из 3-х байтовых – однобайтовыми. MVI M, 5B MHL←5Bh

· Абсолютный – необходимо перейти по какому-то адресу, указанному в команде. STA 0820 M0820←A (GOTO 0000)

· Относительный

Адресное пространство микропроцессора

Состав микропроцессорного комплекта КР580

КР580ВМ (ИК) 80А (Intel 8080) универсальный микропроцессор;

КР580ГФ24 (Intel 8224) – генератор тактовых импульсов;

КР580ВК28 (Intel 8228) – системный контроллер;

КР580ВК38 (Intel 8238) – системный контроллер;

КР580ВА86 (Intel 8286) – шинный формирователь;

КР580ВА87 (Intel 8287) – шинный формирователь с инверсией;

КР580ВВ51 (Intel 8251) – универсальный последовательный порт (UART);

КР580ВВ55 (Intel 8255) – универсальный параллельный порт;

КР580ВР43 (Intel 8243) – расширитель портов;

КР580ВН59 (Intel 8259) – контроллер прерываний;

КР580ВИ53 (Intel 8253) – программируемый таймер;

КР580ВВ79 (Intel 8279) – контроллер клавиатуры и индикации;

КР580ВГ75 (Intel 8275) – контроллер монитора;

КР580ВТ42 (Intel 8242) – контроллер динамического ОЗУ;

КР580ВТ57 (Intel 8257) – контроллер прямого доступа в память;

КР580ВА93 (Intel 8293) – приемопередатчик;

КР580ВГ18 (Intel 8218) – арбитр шины;

КР580ВГ92 (Intel 8292) – контроллер МП канала общего пользования;

КР580ВК91 (Intel 8293) – контроллер МП канала общего пользования;

КР580ИР82 (Intel 8282) – 8-разрядный буферный регистр;

КР580ИР83 (Intel 8283) – 8-разрядный буферный регистр с инверсией.

КЛАССИФИКАЦИЯ МП

Типовая структура

по типу архитектуры

Архитектура – это совокупность средств и возможностей, доступных программисту при программировании.

Микропроцессор: CISC, RISC, микроконтроллеры

CISC – микропроцессор с полным набором команд

Особенности:

* большое число команд (до 250);

* команды имеют формат переменной длины;

* редко имеются команды, выполняющие специальные функции;

* имеются команды, управляющие операндами в памяти;

* каждая из команд реализуется за счет выполнение нескольких микрокоманд МП;

Микрокомандное управление – команды хранятся в ПЗУ, эти команды заносятся в RG управлений, который формирует выходной сигнал обеспечивающий последовательность

* имеются от 6 до 20 различных видов адресации.

RISC – МП с ограниченным набором команд.

Особенности:

- небольшое количество команд простого формата;

- небольшое количество режимов адресации (непосредственная, регистровая, относительная);

- относительно большое число внутренних регистров для исключения обращения к памяти;

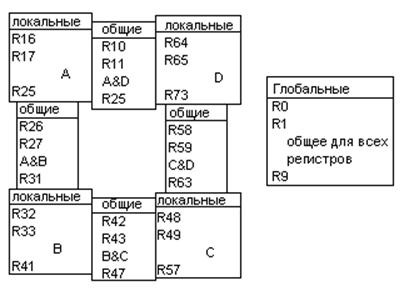

- перекрывающиеся окна регистров;

NGLOBAL+NLOCAL+2*NCOMMON=10+10+6*2=32

- обращение к памяти только с целью загрузки и записи команд;

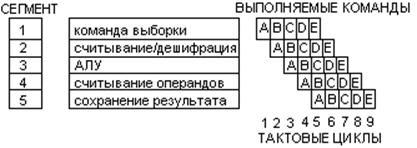

- выполнение команд за 1 такт с использованием конвеиризации (это способ разбиения действия на ряд простых действия, которые используются параллельно);

5 команд × 5 тактов = 25 тактов

- использование конвейера при производстве вычислений;

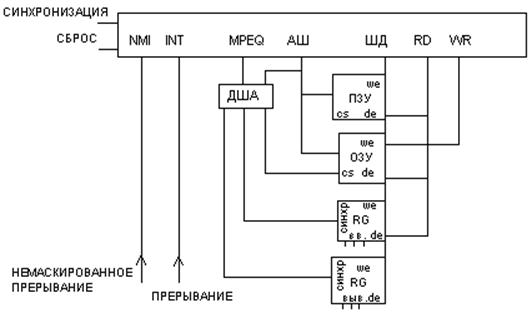

Синхронизация:

- аппаратное или микропрограммное управление.

|

I |

Код операции |

Адрес, регистр или операция вв/выв |

15 14 12 11 0 (биты)

I = 0 для режима прямой адресации

I = 1 для режима косвенной адресации.

Пример аппаратного управления:

МИКРОКОНТРОЛЛЕРЫ – это МП+память, порты ввода/вывода, ЦЫП, АЦП, таймеры и др. устройства (однокристальные ЭВМ).

По числу БИС в микропроцессорах

1) однокристальные

2) многокристальные

3) многокристальные секционные

По назначению

1) Универсальные

2) Специализированные

По виду обрабатываемых входных сигналов

1) Цифровые

2) Аналоговые (принимают через АЦП, обрабатывают и выдают через ЦАП в виде реального масштаба времени или ускоренном)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.