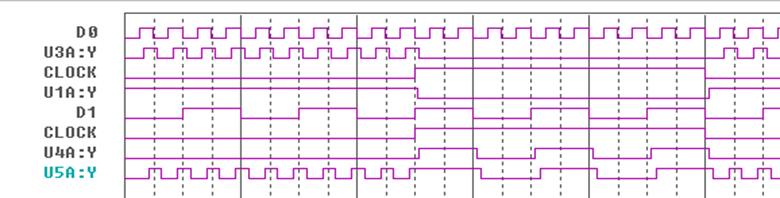

Через некоторое время на экране появятся результаты моделирования в виде временных диаграмм тех сигналов, для которых на схеме были установлены маркеры (рис. 13).

Рис. 13. Временные диаграммы

Их визуальный анализ представляет хорошее средство для усвоения сведений о работе цифровых устройств и контроля правильности разработанного проекта. В отношении примера мультиплексера из рис. 13 можно сделать вывод, что при нулевом значении управляющего сигнала Clock на выход подаётся сигнал D0, а при единичном - D1. На диаграммах можно определить величину времени задержки распространения логических элементов в виде относительного смещения диаграмм, которое нарастает при последовательном прохождении сигнала через элементы.

Приложение1

Порядок выполнения задания на лабораторные работы

4.1. Создать новый проект: Пуск\Программы\ Orcad

New Project\ Name\PC Board Wizard\OK

Enable project simulation![]() \ Next

\ Next

74als.olb\Add\Finish

4.2. Cоздать принципиальную схему в окне Schematic1:Page1:

Select\Part: Разместить компоненты в соответствии со структурным уравнением.

Wire: Соединить

компоненты проводами. ![]() , Net

alias: Присвоить имена входным и выходным переменным

, Net

alias: Присвоить имена входным и выходным переменным

4.3. Присоединить генераторы испытательных сигналов: Part \SOURCSTM \ DigStim1. Задать имена генераторам (двойной щелчёк на предварительном имени)

4.4. Запрограммировать входные воздействия: Выделить генератор мышью, затем правая кнопка\Edit PSpice Stimulus\New Stimulus. Имя 1-го генератора и тип сигнала: Digital\Clock\OK. Установить параметры: Frequency, Duty circle, initial value, time delay. Завершение: Apply\ OK\ Save и закрыть окно редактора. Повторить для остальных генераторов.

4.5. Создать файл с данными для испытаний: PSpice\ New Simulation Profile\ имя файла (проекта)\ Simulation Settings. Закладка: Analysis\Time Domain\Run to time\ 2000ns. Закладка: Stimulus\ имя файла (проекта)\ Add to Design\Apply\OK

4.6. Проведение испытаний: Разместить на принципиальной схеме маркеры Voltage\Level Marker. Запустить программу испытаний: Run

4.7. Провести анализ результатов испытаний и продемонстрировать их преподавателю.

Приложение 2

Некоторые особенности моделирования последовательностных цифровых устройств

Главная особенность проектирования и испытания последовательностных устройств состоит в наличии в их составе элементов памяти, роль которых в электронных схемах выполняют триггеры. Наиболее широко используются триггеры JK- типа, обладающие свойством универсальности, и D-триггеры. Оба типа триггеров представлены в библиотеках пакета Orcad.

Входы триггеров J,K,D будем называть информационными. Значительное удобство при разработке схем представляет наличие интегральных схем триггеров с дополнительными логическими возможностями в отношении информационных входов. Так, в библиотеке 7400 имеются триггеры с одиночными J и K входами (74107,7411), J-K триггер 74109, у которого вход K является инверсным, и несколько триггеров с тремя входами по J и по K, объединённых в тройках логической операцией И (74110,7472). В других триггерах этой группы в тройках имеется по одному инверсному входу (74105,7470), в триггере 74104 имеется дополнительный вход, общий для J и K (т.е. реализующий счётный режим). В библиотеках 74ALS и 74 LS ассортимент JK –триггеров беднее. Схемы 74ALS 109,112, 74LS 109, 112, 113, 73 и 76 представляют одиночные JK- триггеры, в том числе с инверсным K входом, а в корпусе 74 LS114 находятся два JK- триггера с одиночными входами.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.