System Debug_Lab3. Исследование и отладка генератора сигналов сложной формы средствами системной отладки Quartus II.

Системные требования: САПР Quartus II V9.0 и выше; лабораторный стенд DiLaB1 с подключенной платой Cyclone II.

Базовые знания: курс Схемотехника, знание раздела средства системной отладки пакета Quartus II в файле System_debug.pdf папки System_debug.

Трудоемкость работы: 3 часа (1 час С1 и 2 часа на выполнение исследований в лаборатории).

Цель работы:

В работе синтезируется и исследуется генератор сигналов сложной формы на основе ПЗУ. Структурная схема такого генератора представлена на рис.1. Исследование включает в себя тестирование прототипа, реализованного на лабораторном стенде.

Рис.1.

В состав генератора входят счетчики Divider и Counter_ROM, обеспечивающие перебор адресов ПЗУ Mem_ROM с циклом повторения, позволяющим наблюдать сигналы с помощью светодиодов. Система выполнена как полностью синхронная и работает с тактовой частотой 25МГц. В ПЗУ Mem_ROM загружаются данные, которые соответствуют сложному периодически повторяющемуся сигналу в соответствии с заданием. Данные с выхода ПЗУ Mem_ROM поступают на выходы Out[7..0], не имеющие физического назначения на выводы используемой микросхемы (Virtual Pin). Логический 0 на выходе led_en разрешает работу светодиодов LED[8..1]. Сами светодиоды будут использоваться в работе для вывода и наблюдения тестируемых внутренних сигналов при использовании LAI и Signal Probe.

Проект LAI_ISMCE с элементами схемы рис.1 реализован в папке ../SystemDebug_Lab3. Разводка выводов проекта выполнена.

Программа работы

Откройте созданный проект LAI_ISMCE, расположенный в папке <Ваша рабочая папка>\ System Debug \ SystemDebug_Lab3. В папке проекта уже содержатся рабочие проектный файл верхнего уровня LAI_ISMCE.bdf. Для проекта выполнена разводка выводов и сделаны необходимые установки для компиляции.

1.1. Откройте проект и доработайте схему:

– на основе мегафункции LPM_Counter реализуйте счетчик Divider (направление счета определите в соответствии с заданием). Полученный символ разместите в указанном на схеме месте.

– на основе мегафункции LPM_ Counter реализуйте адресный счетчик Counter_ROM. Полученный символ разместите в указанном на схеме месте.

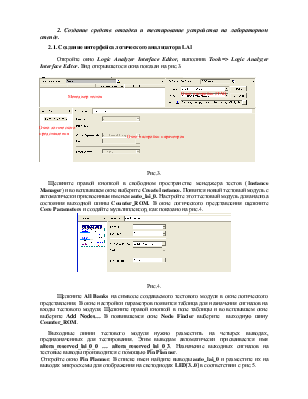

– на основе мегафункции ROM: 1-PORT реализуйте ПЗУ Mem_ROM. Для этого откройте MegaWizard и в папке Memory Compiler выберите ROM: 1-PORT. На третьей странице настройки задайте разрядность ― 8 бит, число слов ― 64. Оставив остальные настройки без изменения, перейдите на четвертую страницу настроек, на которой отключите выходные регистры блока памяти. На пятой странице настроек задайте имя файла инициализации памяти (необходимо будет далее в п.2 создать файл <имя файла>.mif, который обеспечит получение сигнала требуемого вида) и разрешите доступ ISMCE к создаваемому блоку памяти. Закончите настройку. Полученный символ должен иметь вид, показанный на рис.2.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.