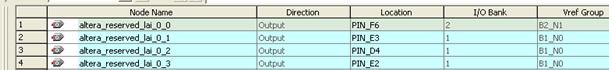

Откройте окно Pin Planner. В списке имен найдите выводы auto_lai_0 и разместите их навыводах микросхемы для отображения на светодиодах LED[3..0] в соответствии с рис.5.

Рис.5.

Компиляция проекта, программирование и контроль работы устройства средствами LogicAnalyzerInterface.

Откройте окно Assignments => Settings => Logic Analyzer Interface. Убедитесь, что работа LAI разрешена. В окне Assignments => Settings => CompilationProcessSettings => IncrementalCompilationsубедитесь, что инкрементальная компиляция отключена.Выполните компиляцию. В окне Progect Navigator посмотрите аппаратурные затраты для реализации тестовых модулей LAI. Результаты зафиксируйте в отчете (см. табл. п.1.3).

Откройте файл lai1.lai. В окне настройки JTAG выполните необходимые установки и загрузите проект в FPGA лабораторного стенда DiLab1.

Выберите в окне менеджера тестов тестовый модуль auto_lai_0 (в окнах логического представления и настройки параметров отображаются настройки auto_lai_0). Щелкните правой кнопкой по Bank_0 в окне логического представления (Logical View). На всплывшем окне щелкните строчку Connect Bank. По состоянию светодиодов LED[3..0] убедитесь в правильности работы устройства. Повторите коммутацию другого банка.

2.2. Исследование проекта средствами SignalTap II.

Откройте окно настройки логического анализатора SignalTap II (Tools / SignalTap II Logic Analyzer). Выполните настройку логического анализатора для исследования генератора сигналов сложной формы:

– в окне задания наблюдаемых сигналов вызовите Node Finder выберите для наблюдения , выходные сигналы счетчика адреса Counter_ROM и памяти (Out[7..0]) счетчика. В столбце Trigger Conditions, установите удобные условия захвата Basic.

– В окне задания параметров (Signal Configuration): сигнал Clock ― старший разряд счетчика Divider; объем выборки 1К. Остальные установки оставьте без изменения.

– Выполните компиляцию проекта. Определите аппаратурные затраты на реализацию отладочных средств и самого генератора сигналов сложной формы. Сравните с аппаратурными затратами в п.2.2.

Откройте окно логического анализатора. В окне настройки JTAG выберите используемое средство загрузки, загружаемый файл и запустите программирование.

Выполните проверку работы устройства в системе-прототипе:

– Задайте режим непрерывной работы логического анализатора. Задайте формат отображения шин Unsigned Bar Chart и убедитесь в работоспособности устройства сравнением формы реализованного сигнала с требуемой в задании.

2.3. Исследование и отладка работы проекта средствами встроенного редактора системной памяти

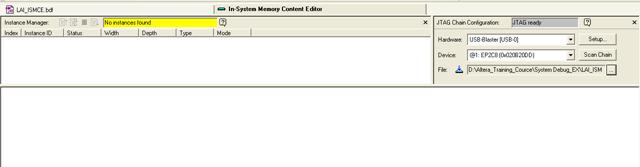

Откройте окно In System Memory Content Editor, выполнив действия, как показано на рис.6.

Рис.6.

Вид открывшегося окна In System Memory Content Editor приведен на рис.7.

|

Окно настройки JTAG |

|

Менеджер тестирования |

|

Окно данных |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.