Рис.2.

Разместите этот символ в указанном месте схемы LAI_ISMCE.bdf.

1.2. Создайте файл инициализации памяти <имя файла>.mif.

– откройте новый файл File/ New/ Memory Files/ Memory Initialization File, указав требуемую разрядность и число слов. Используя опции меню View, настройте окно для удобного ввода данных.

– Введите данные, обеспечивающие формирование сигнала в соответствии с заданием.

– Сохраните файл как <имя файла>.mif.

1.3. Выполните полную компиляцию устройства. Проанализируйте предупреждения компилятора. Запишите аппаратурные затраты и временные характеристики синтезированного проекта, а также время, необходимое для компиляции. Результаты занесите в таблицу:

|

Блок проекта |

Аппаратурные затраты |

F max |

Время компиляции |

|

Divider |

|||

|

Counter_ROM |

|||

|

Mem_ROM |

2. Создание средств отладки и тестирование устройства на лабораторном стенде.

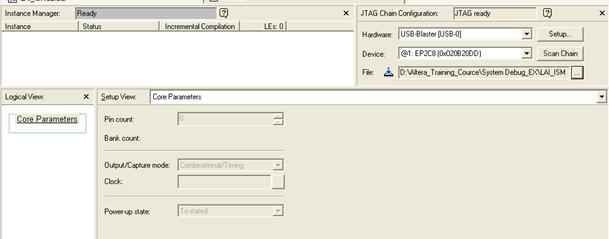

2.1. Создание интерфейса логического анализатора LAI

|

Менеджер тестов |

|

Окно настройки JTAG |

|

Окно логического представления |

|

Окно настройки параметров |

Рис.3.

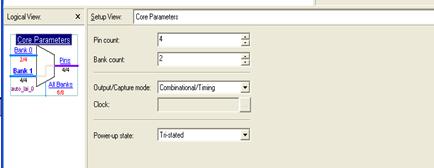

Щелкните правой кнопкой в свободном пространстве менеджера тестов (Instance Manager) и во всплывшем окне выберите Create Instance. Появится новый тестовый модуль с автоматически присвоенным именем auto_lai_0. Настройте этот тестовый модуль для анализа состояния выходной шины Counter_ROM. В окне логического представления щелкните Core Parameters и создайте мультиплексор, как показано на рис.4.

Рис.4.

Щелкните All Banks на символе создаваемого тестового модуля в окне логического представления. В окне настройки параметров появится таблица для назначения сигналов на входы тестового модуля. Щелкните правой кнопкой в поле таблицы и во всплывшем окне выберите Add Nodes… В появившемся окне Node Finder выберите выходную шину Counter_ROM.

Выходные линии тестового модуля нужно разместить на четырех выводах, предназначенных для тестирования. Этим выводам автоматически присваивается имя altera_reserved_lai_0_0 … altera_reserved_lai_0_3. Назначение выходных сигналов на тестовые выводы производится с помощью Pin Planner.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.