Архітектура.

Введення

Висока ефективність мікроконтролерів PlCmicro дістається за рахунок архітектури ядро, подібна архітектура звичайно застосовується в RISC мікропроцесорам

Основні особливості архітектури мікроконтролерів PlCmicro:

• Гарвардська архітектура;

• Довге слово команди;

• Команда складається з єдиного слова;

• Конвеєрна обробка команд.

• Команди виконуються за один машинний цикл.

• Невелике число команд.

• Файлова структура даних;

• Всі команди ортогональні(симетричні).

На малюнку показана а загальна структурна схема мікроконтролерів PlCmircro середнього сімейства.

Гарвардська архітектурі:

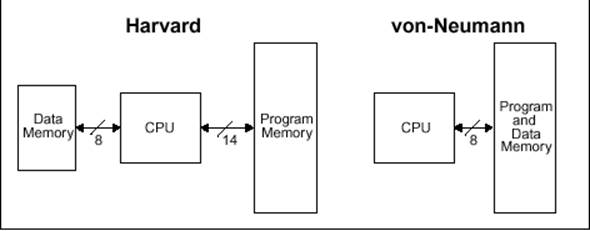

У гарвардській архітектурі розділена пам'ять програм і пам'ять даним Звертання до пам'яті відбувається по окремих шинах адреси й даним, що значно підвищує продуктивність процесора в порівнянні із традиційною архітектурою.

У мікроконтролерах із традиційною архітектурою ядра команди й дані запитуються по однієї й тій же шині. Щоб виконати вибірку команди необхідно зробити кілька запитів по 8-розрядній (або кратної 8 розрядам) шині. Потім (якщо необхідно) запросити дані, виконати команду й зберегти результат. Як може бути замічено, шина із традиційною архітектурою ядра значно завантажена.

У мікроконтролерах з гарвардською архітектурою ядра вибірка команди відбувається за один цикл (всі команди 14 - розрядні) При звертанні до пам'яті програм можна виконати запис або читання даних т.як пам'ять даних підключена до ядра мікроконтролера по окремій шині. Роздільні шини доступу до пам'яті програм і до пам'яті даних дозволяють виконувати поточну команду й робити вибірку наступної команди, організувати конвеєрну обробку команд. Порівняння гарвардської й традиційної архітектури показано на малюнка

Довге слово команди.

Розрядність команд мікроконтролера трохи більше чим 8-розрядна шина пам'яті даних. Це стали можливий через роздільні шини доступу до пам'яті програм і пам'яті даних. Поділ шин доступу до різного видам пам'яті дозволяє довільно вибирати розрядність команд мікроконтролера (не кратне 8-розрядній шині даних) що у свою чергу дає можливість ефективно використати пам'ять програм й оптимізувати розрядність шини програм архітектурним вимогам мікроконтролера.

Команда складається з єдиного слова:

Всі команди мікроконтролерів PIC16CXXX однослівні 14 - розрядні. 14 - розрядна шина доступу до пам'яті програм дозволять виконати вибірку 14 - розрядної команди за один машинний цикл мікро контролера. При використанні однослівних команд число слів у пам'яті програм рівняється максимальному числу команд програми мікроконтролера. Це означає, що всі комірки пам'яті мають силу команди

Як правило, у традиційній архітектурі більшість команд багатобайтні. Мікроконтролер, що має 4 Кбайт пам'яті, містить приблизно 2К команд. Коефіцієнт використання пам'яті приблизно дорівнює 2:1 і залежить від конкретного додатка. Оскільки кожна команда може складатися з декількох байтів, те немає ніякий гарантій, що кожна комірка пам'яті програм має силу команди.

Конвеєрна обробка команд:

Конвеєрна обробка команд складається із двох стадій вибірка команди з пам'яті виконання команди. Вибірка команди відбувається в перший машинний цикл Тсy, а виконаються команда в другому машинному циклі Тсy. Однак, через одночасну вибірку поточної команди й виконання попередньої в кожному машинному циклі Тcy, відбувається вибірка й виконання команд.

Команди виконуються за один машинний цикл.

Повна вибірка команд відбувається за один машинний цикл (Tcy) через те, що шина доступу до пам'яті програм 14 - розрядна. Кожна команда містить всю необхідну інформацію й виконується за один машинний цикл. При виконанні команди може виникати затримка в один машинний цикл, якщо результат команди змінює вміст лічильника команд PC. Затримка в один машинний цикл необхідний для вибірки нової команди, що повинна бути виконана наступної.

Невелике число команд:

Коли система команд добре пророблена й команди ортогональні(симетричні), те потрібне менше число команд для рішення всіх необхідних завдань. З меншим числом команд вивчення мікроконтролера значно спрощується.

Файлова структура даних;

Звертання до регістрів пам'яті даних можна виконати прямою або непрямою адресацією. Всі регістри спеціального призначення, включаючи лічильник команд PC відображається в пам'яті даних

Всі команди ортогональні(симетричні):

Ортогональна система команд дає можливість виконати будь-яку операцію з будь-яким регістром пам'яті даних прямій або непрямій адресації. В ортогональній системі команд мала кількість "спеціальних команд", що спрощує вивчення й програмування мікроконтролерів не гублячи ефективності коду програми. У мікроконтролерах середнього сімейства використається тільки дві не ортогональні команди, що реалізують

особливості ядра:

Команда SLEEP - переводить мікроконтролер у режим зниженого енергоспоживання

Команда CLRWDT - підтверджує нормальну роботу мікроконтролера запобігаючи скиданню по переповненню сторожового таймера WDT

Конвеєрна вибірка й виконання команд

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.