Цикл виконання команди складається із чотирьох тактів Q1, Q2, Q3 й Q4 Вибірка наступної команди й виконання поточної сполучені за часом, таким образам, виконання команди відбувається за один цикл. Якщо команда змінює лічильник команд PC (команди розгалуження, наприклад GOTO), то необхідно два машинних цикли, для виконання команди.

Цикл вибірки команди починається зі збільшення лічильника команд PC у такті 01

У циклі виконання команди, код завантаженої команди, міститься в регістр команд IR на такті Q1. Декодування й виконання команди відбувається в тактах ПРО2, Q3 й Q4. Операнд із пам'яті даних читається в такту ПРО2, а результат виконання команди записується в такті Q4.

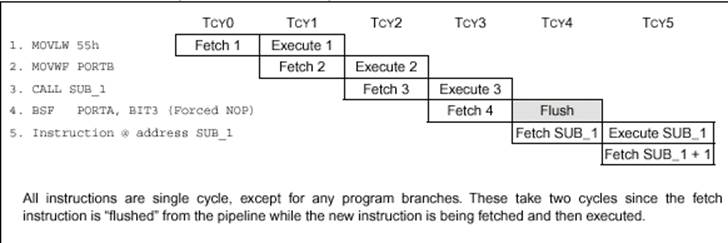

У прикладі показані дві стадії конвеєрної обробки команд для представленої послідовності. У циклі TCY0 відбувається вибірка першої команди з пам'яті програм. На циклі TCY1 перша команда виконується, а друга команда вибирається з пам'яті програм. Протягом циклу TCY2 друга команда виконується, а треті вибирається з пам'яті програм. На циклі TCY3 відбувається вибірка четвертої команди й виконується команда третя команда (CALL SUВ_1). Коли завершується виконання третьої команди CPU завантажує адресу четвертої команди у вершину стека й змінює лічильник команд PC на адресу SUВ_1.Це означає, що команда завантажена в циклі TCY3, повинна бути вилучена з конвеєра. Протягом циклу Тсу4 четверта команда віддаляється з конвеєра (виконується порожній цикл NOP) і відбувається вибірка команди за адресою SUВ_1. У циклі TCY3, виконується команда п'ять і вибирається з пам'яті програм команда з адресою SUB_1 + 1

Всі команди виконуються за один цикл, крім команд розгалуження Команди розгалуження вимагають два машинних цикли, т до необхідно видалити попередньо обрану команду з конвеєра Під час видалення вибирається нова команда, а потім вона виконується в наступному машинному циклі.

Введення

Центральний Процесорний Пристрій (ЦПП) призначено для детектирования команд, розташованих у пам'яті програм, і керування роботою мікро контролера. Більшість команд мікроконтролера звертаються до комірок пам'яті даних. Для роботи з пам'яттю даних потрібне арифметико-логічний пристрій (АЛП). АЛП виконує арифметичні, логічні операції й управляє прапорами стану (прапори стани розташовані в регістрі STATUS) Виконання деяких команд приводить до зміни бітів стану залежно від отриманого результату

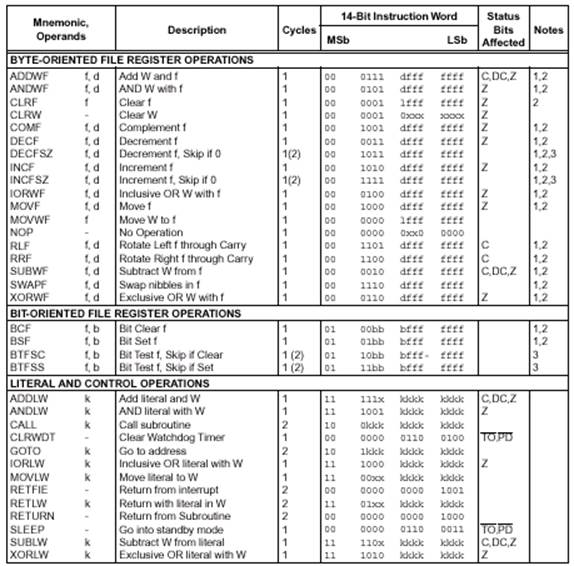

У таблиці приведені коди команд, що підтримує ЦПП:

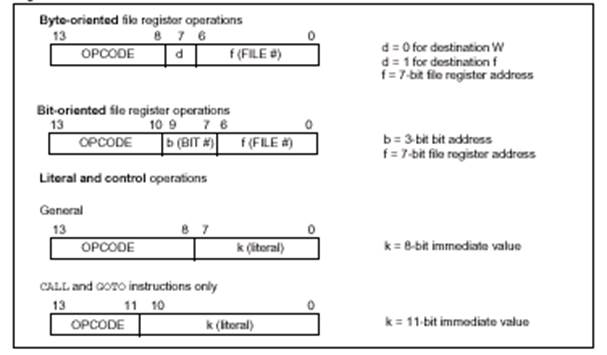

Загальний формат команд мікроконтролерів середнього сімейства:

Всі команди мікроконтролерів середнього сімейства можуть бути розділені на чотири основних групи. Код операції команди змінюється від 3 біт до 6 біт, що дозволяє реалізувати 35 команд.

Центральний Процесорний Пристрій (ЦПП)

ЦПП можна розглядати як "мозок" мікроконтролера. ЦПП відповідає за вибірку команди з пам'яті програм, її детектування й виконання. Іноді ЦПП працює разом з АЛП щоб виконати арифметичні або логічні операції. ЦПП управляє шиною адреси пам'яті програм і пам'яті даних, а також звертанням до стеку.

Такти виконання команд:

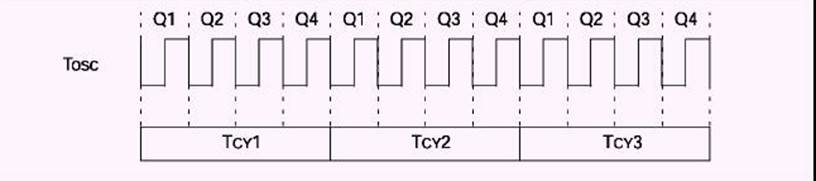

Кожен цикл команди (ТCY) складається із чотирьох

тактів (Q1-Q4) Такт Q дорівнює по тривалості періоду тактового генератора (ТOSC).

Такти Q забезпечують тверду синхронізацію декодування, читання даних, обробки

даних,

запису результату для кожного циклу команди На діаграмі показане

співвідношення тактів Q до циклу команди:

Цикл команди (ТCY), що складає з 4-х тактів, узагальнено виглядає в

такий спосіб:

Q1:Детектування команди або примусовий пустий операнд (NQP)

Q2:Операція читання даних або відсутність операції

Q3:Обробка даних

Q4:Операція запису даних або відсутність операції

Арифметико-логічний Пристрій (АЛП)

Мікроконтролери PIсmicro MCU містять 8-розрядный універсальний арифметичний модуль (АЛП) і 8 - розрядний робочий регістр (W). АЛП виконує арифметичні й булєві операції між робочим регістром і будь-яким регістром пам'яті даних.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.