Операція збереження значення регістрів звичайно позначається 'PUSH', а відновлення значення регістрів позначається "POP" Зверніть увагу що PUSH, POP не є мнемонікою команд, а лише позначають дію, що може бути виконано послідовністю команд. Для спрощення тексту програми можна ці сегменти року програми представити у вигляді макросів

Введення

Модуль синхронного послідовного порту (SSP) може використатися для зв'язку з периферійними мікросхемами або іншими мікро контролерами. Периферійними мікросхемами можуть бути: ЕЕPROM пам'ять, сдвигові регістри, драйвери ЖКИ, АЦП й ін. Модуль SSP може працювати в одному із двох режимах:

· Послідовний периферійний інтерфейс (SPI):

· Inter-Integrated Circuil (I2C)

- веденої режим:

-контроль стану портів вводу/виводу для виявлення бітів START, STOP з метою спрощення програмного забезпечення в режимі ведучого й при конкуренції на шині.

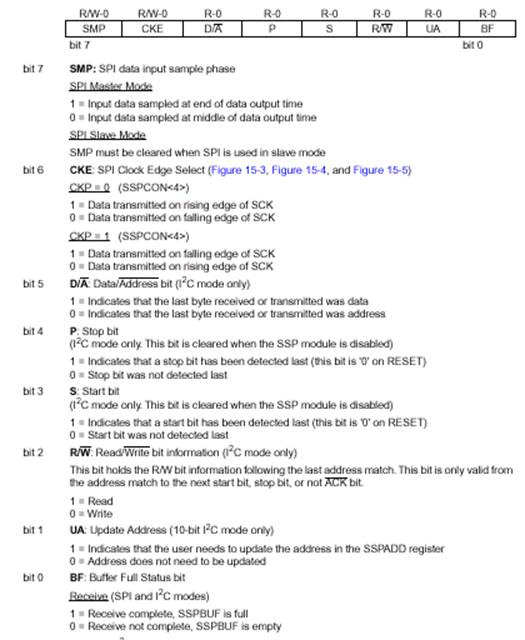

sspstat: регістр статусу модуля SSP

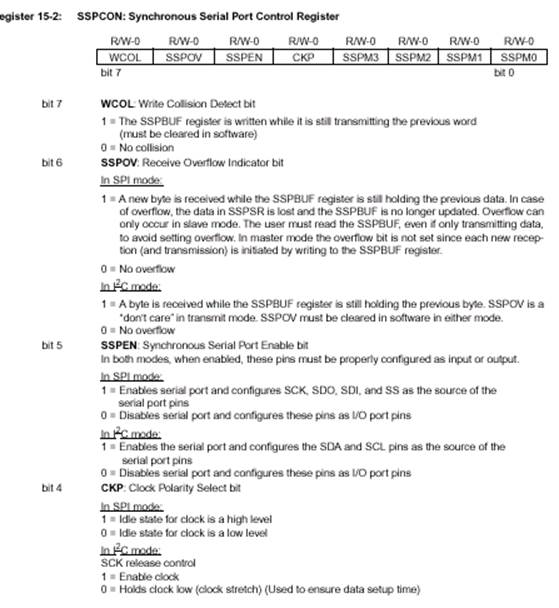

sspcon: регістр управління модуля SSP

Режим SP1

В SPI режимі можливі одночасний синхронний прийом і передача 8-розрядних даних. Модуль SSP підтримує чотири режими SPI з типовим використанням трьох висновків мікро контролера. У режимі ведучого SPI легко реалізувати інтерфейс Microwire .

• Вхід послідовних даних (SDI),

• Вихід послідовних даних (SDО),

• Тактовий сигнал (SCK)

Додатково може бути задіяний четвертий висновок для роботи в режимі відомого:

• Вибір відомого (-SS).

Робота модуля SSP у режимі SPI

При ініціалізації SPI необхідно визначити параметри роботи модуля SPI бітами SSPCО(<5:0>), SSPSTAT<7:6>. Керуючі біти визначають наступні параметри роботи

• Ведучий режим (SCK вихід)

• Відомий режим (SCK вхід)

• Полярність тактового сигналу (пасивний рівень SCK):

• Фаза вибірки вхідних даних,

• Активний фронт тактового сигналу (передній, задній),

• Частота тактового сигналу (тільки в ведучому режимі);

• Режим вибору відомого (тільки в режимі відомого)

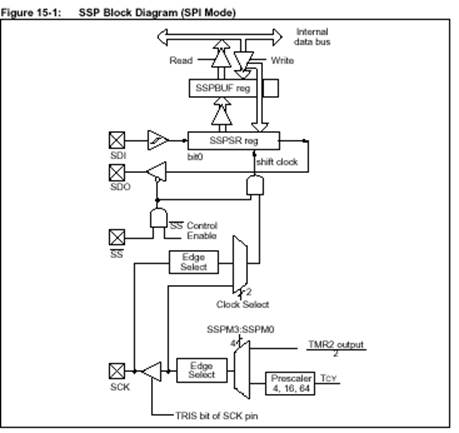

Структурна схема SSP в SPI режимі

Модуль SSP складається на прийомного/передавального регістра зрушення (SSPSR) і буферного регістра (SSBUF). У регістрі SSPSR виконується зрушення данних з/у мікроконтролер старшим бітом уперед. У регістрі SSPBUF зберігаються записані дані поки не будуть отримані нові. Прийнявши 8 біт даний у регістр SSPSR вони переписуються в SSPBUF, встановлюється в '1' прапор повного прийомного буфера BF (SSPSTAT<0>) і прапор переривання SSPIF. Подвійна буферизація прийнятих даних дозволяє приймати наступний байт до читання попередній Будь-який запис у регістр SSPBUF під час виконання операції прийому/передами даних буде ігнорована, при цьому встановлюється в '1' прапор WCOL (SSPCON<7>). Користувач повинен програмно скинути біт WCOL в '0', щоб була можливість проверни виконання запису в регістр SSPBUF. При прийомі даних у режимі SPI регістр SSPBUF повинен бути прочитаний до моменту закінчення прийому наступного байта. Біт статусу прийомного буфера BF (SSPSTAT<0>) указує на одержання нового байта даних. Біт BF апаратно скидається в '0' при читанні регістра SSPBUF Прийняті дані можуть бути недостовірними, якщо режим SPI використається тільки для передачі даних. Переривання від модуля SSP використаються для визначення завершення прийому/передачі даних (у підпрограмі обробки переривань необхідно прочитати/записати регістр SSPBUF). Якщо не планується використати переривання від модуля SSP то необхідно передбачити програмну перевірку виконання запису в регістр SSPBUF для передачі даних.

Модуль USART.

USART - це один із модулів послідовного порту вхіду/вихіду (має істотні відмінності від модуля SSP), що може працювати в повному-дуплексному асинхронному режимі для зв'язку з терміналами, персональними комп'ютерами або синхронним напівдуплексним режимом для зв'язку з мікросхемами ЦАП, ДЦП, послідовними EEPRО і т.д.

USART може працювати в одному із трьох режимів

Асинхронний, повний дуплекс Провідний синхронний, напівдуплекс Ведений синхронний, полудуллекс

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.