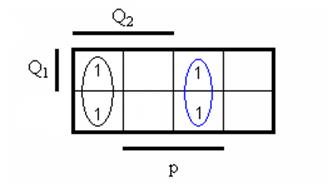

9. Логический синтез преобразователя множителя (ПМ)

Преобразователь

множителя (ПМ) (рис.9) служит для исключения из множителя диад 11, заменяя их

на триады ![]() .

.

Рис. 9. Схематическое изображение ПМ

Таблица 25 представляет собой таблицу истинности для ПМ.

Таблица истинности для ПМ. Таблица 25

|

Входы ПМ |

Выходы ПМ |

|||||

|

Q1 |

Q2 |

p |

y |

y1 |

y1 |

z |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

![]()

![]()

![]()

![]()

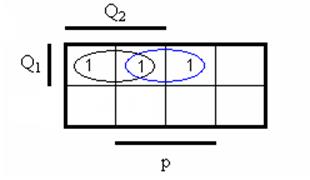

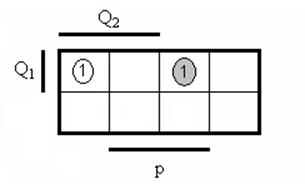

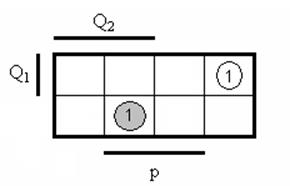

Минимизация y, z,y1,y2 с помощью карт Карно-Вейча:

Выход y:

![]()

Рис. 10.Карта Карно - Вейча для выхода y

![]()

Выход z:

![]()

Рис. 11.Карта Карно - Вейча для выхода z

![]()

Выход y1:

![]()

Рис. 12.Карта Карно - Вейча для выхода y1

![]()

Выход y2:

![]()

Рис. 13.Карта Карно - Вейча для выхода y2

![]()

Функциональная схема преобразователя множетеля находится на рисунке 14.

Рис. 14.

Функциональная схема преобразователя множетеля.

10. Блок порядков

Блок порядков предназначен для получения порядка результата в зависимости от типа операции.

Если устройство работает как умножитель, то на вход h поступает 0, в регистр 1 заносится порядок множителя, в регистр 2 – порядок множимого, на входы F1 и F2 поступает 0. На входы ОЧС поступает значение регистра 2, т.е. порядок множителя, и затем суммируется со значением регистра 1, т.е. порядок множимого. Управляющее устройство (УУ) заносит полученный результат в регистр результата.

Если устройство работает как сумматор, то на вход h поступает 1, в регистр 2 записывается значение порядка второго слагаемого, в регистр 1 – порядок первого, на входы F1 и F2 ФДК приходит 1, происходит смена знака порядка множителя. На первом такте работы происходит вычитание из значения регистра 1 значения регистра 2. УУ анализирует знак результата и выбирает, какой из порядков заносится в регистр результата (если знак 0 – то первого слагаемого, если 1 - второго). На последующих тактах работы происходит запись 1 в регистр 2(если разность положительна) или -1 (если разность отрицательна), инвертирование этого значения в ФДК и сложение его с полученной на предыдущем такте разностью, хранящейся в регистре 1. Под действием сигналов УУ после каждого такта работы происходит сдвиг мантиссы второго слагаемого (если знак результата равен 0) или первого (если знак равен 1). Работа продолжается до получения нуля в регистре 1 в результате очередного вычитания.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.