|

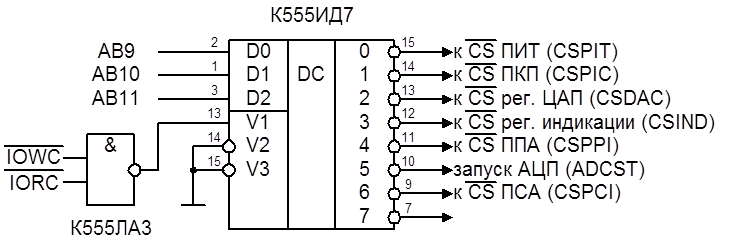

Рисунок 6. Схема дешифрации портов.

Программируемый параллельный интерфейс в данной системе реализован на БИС КР580ВВ55А [2,3]. Данная БИС в своем составе имеет 3 8-разрядных параллельных порта A, B и С, способных работать как на ввод, так и на вывод. Старшая и младшая тетрады порта С могут программироваться раздельно.

С точки зрения системного модуля БИС ППА представляет собой 4 двунаправленных 8-битных порта. Выборка микросхемы осуществляется низким уровнем на входе CS, режим обмена (запись/чтение) задается сигналами на линиях RD и WR (активный уровень низкий), внутренний же адрес порта определяется комбинацией сигналов на входам A0 и A1.

В данной системе используется статический режим работы всех трех портов (режим 0), при этом порты А, В и младшая половина С программируются на ввод, а старшая половина С – на вывод. Назначение портов пояснено при описании структурной схемы МПС.

Последовательный интерфейс КР580ВВ51А [2,3] в этой разработке используется для организации связи с ЭВМ. Функционально БИС программируемого связного адаптера (ПСА) представляет собой законченный модуль последовательного интерфейса, поэтому для подключения ее к системной магистрали не требуются какие-либо дополнительные схемы.

При запуске БИС инициализируется на асинхронный режим обмена с коэффициентом деления частоты 1:16, что при тактировании приемника и передатчика частотой 62,5 кГц обеспечивает скорость обмена около 3900 бод. Частота 62,5 кГц снимается с выхода делителя частоты с коэффициентом деления 32, выполненного на счетчике К555ИЕ19 [4]. Тактирование схемы управления БИС осуществляется от сигнала CLK (2 МГц).

Для выдачи сигналов индикации на пульт управления используем ТТЛШ регистр К555ИР22 [5], представляющий собой простейший порт вывода. При единичном уровне на входе разрешения E защелкивание сигналов с шины данных происходит по фронту стробирующего сигнала на входе C. Для обеспечения сопряжения прямого входа C с инверсным выходом дешифратора портов в схему введен инвертор.

Подсистема аналогового сопряжения содержит следующие основные узлы:

- цифро-аналоговый преобразователь (ЦАП) – предназначен для формирования управляющего воздействия Y4

- аналого-цифровой преобразователь (АЦП) – предназначен для преобразования сигналов аналоговых датчиков V1-V3 в цифровую форму для передачи в МПС

- аналоговый коммутатор (АК) – предназначен для коммутации аналоговых входов V1-V3 на АЦП

В качестве ЦАП используем перемножающий 12-разрядный ЦАП (ПЦАП) К572ПА2 [7]. БИС ПЦАП выполнена по КМОП - технологии с сигналами, совместимыми с уровнями ТТЛ. Для цифро-аналогового преобразования используются токовые ключи, коммутирующие источники тока на матрицу R-2R. Дифференциальная нелинейность преобразования БИС не превышает 1% от шкалы. Время установления выходного сигнала – не более 5 мкс. Для формирования аналогового сигнала данному ПЦАП необходим внешний операционный усилитель, в качестве которого используем ОУ с малыми входными токами и внутренней коррекцией КР140УД6. Микросхема способна работать от однополярного источника +15В и не требует внешних навесных элементов.

Из 12 разрядов ЦАП используем только 8 старших разрядов, а на остальные входы подаем уровень логического нуля.

ЦАП К572ПА2 имеет в своем составе два внутренних регистра-защелки, что позволяет обойтись без внешнего регистра и подключить ЦАП прямо к шине данных. Управление регистрами осуществляется через статические входы C1 и C2. Регистр 1 принимает информацию с шины данных, а регистр 2 передает ее на токовые ключи. Таким образом, используя один инвертор, можно организовать конвейерное прохождение данных через оба регистра и их хранение при отсутствии обращения к микросхеме. При неактивном высоком уровне на линии CSDAC (выбор ЦАП) регистр 1 БИС будет повторять информацию на шине данных, а при переходе выборе микросхемы ПЦАП (срезе CSDAC) данные из регистра 1 перепишутся в регистр 2 и защелкнутся там (рисунок 7).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.